**APRIL 1982**

LSI-11 Bus Interface Chips and Accessories

# digital

TECHNICAL VOLUME GROUP

77 REED ROAD, HUDSON, MA 01749

The information in this document is subject to change without notice, and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for errors that may appear in this document.

Copyright . 1979, 1981, 1982 by Digital Equipment Corporation

tario de la constante de la co

# CONTENTS

| ORDERING INFORMATION                                   | ٧    |

|--------------------------------------------------------|------|

| INTRODUCTION                                           | 1    |

| BRIEF SPECIFICATIONS OF INTEGRATED CIRCUITS            | 3    |

| DC003 INTERRUPT LOGIC                                  |      |

| Description                                            | 4    |

| Logic Diagram                                          | 4    |

| Pin Diagram                                            |      |

| Pin/Signal Description                                 | 5    |

| Electrical Characteristics                             | 7    |

| Timing Diagrams                                        | . 12 |

| DC004 PROTOCOL LOGIC                                   |      |

| Description                                            | . 13 |

| Logic Diagram                                          | . 13 |

| Pin Diagram                                            | . 13 |

| Pin/Signal Description                                 | . 14 |

| Electrical Characteristics                             | . 16 |

| Timing Diagram                                         | . 21 |

| Loading Configurations                                 |      |

| Timing vs. Loading Table                               |      |

| DC005 TRANSCEIVER LOGIC                                |      |

| Description                                            | . 23 |

| Logic Diagram                                          | . 24 |

| Pin Diagram                                            |      |

| Pin/Signal Description                                 |      |

| Electrical Characteristics                             | . 26 |

| Timing Diagrams                                        |      |

| DC006 WORD COUNT/BUS ADDRESS LOGIC                     |      |

| Description                                            | . 33 |

| Logic Block Diagram                                    | . 33 |

| Logic Diagram                                          |      |

| Pin Diagram                                            |      |

| Truth Table                                            |      |

| Pin/Signal Description                                 |      |

| Electrical Characteristics                             |      |

| Input Voltage Waveform                                 |      |

| Output Voltage Waveform                                |      |

| Timing Diagram                                         |      |

| Setup Time/Pulse Width Switching Characteristics Table |      |

| Switching Characteristics Table                        |      |

# Montagon Company (1997) For the Company (1997) State of the Company (1997) State of the Company (1997)

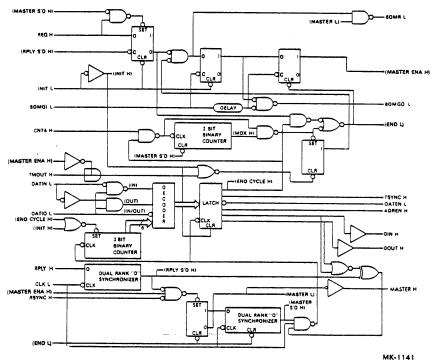

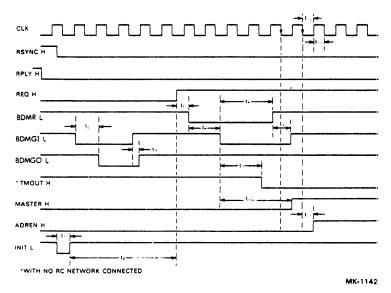

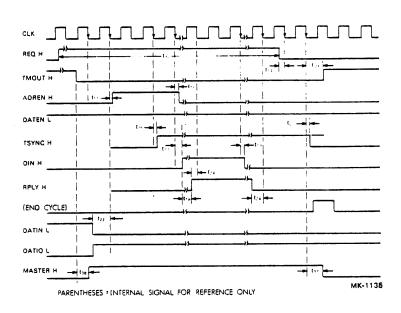

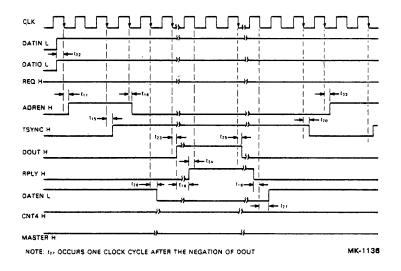

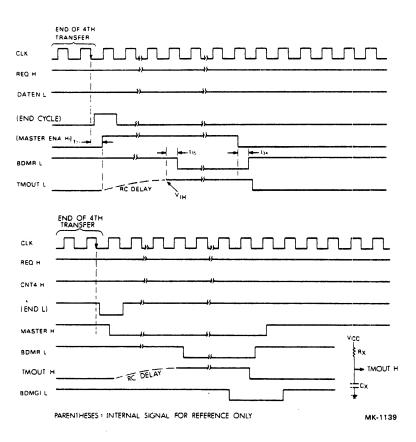

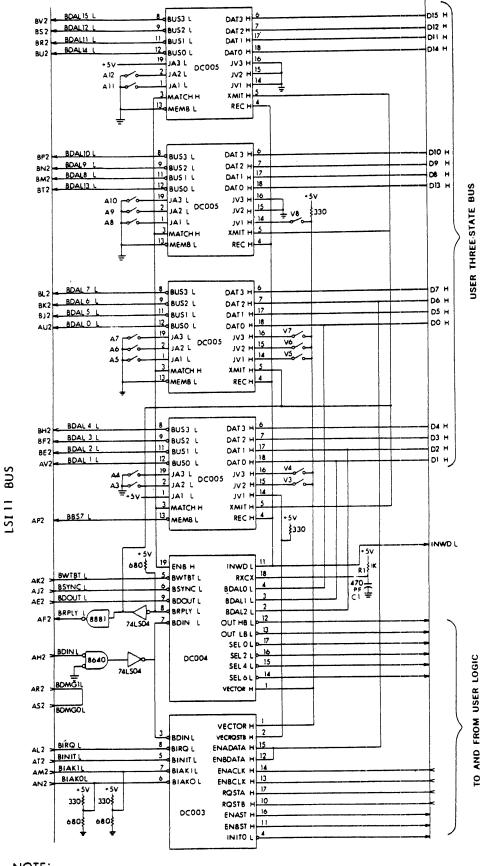

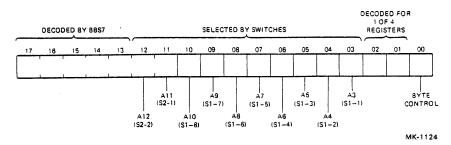

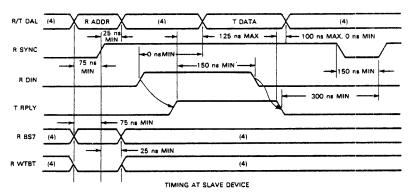

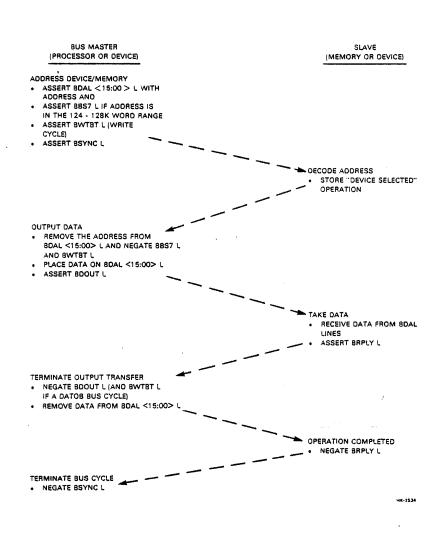

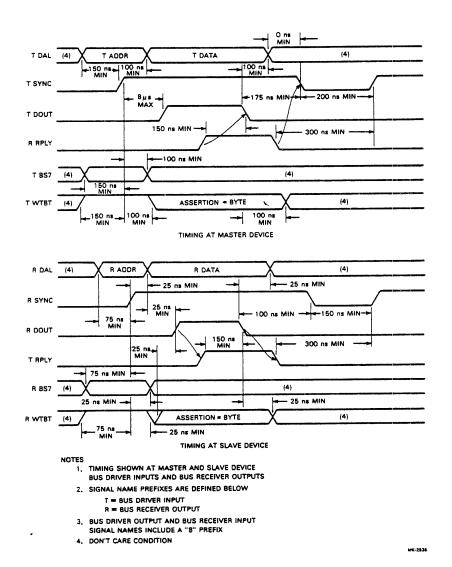

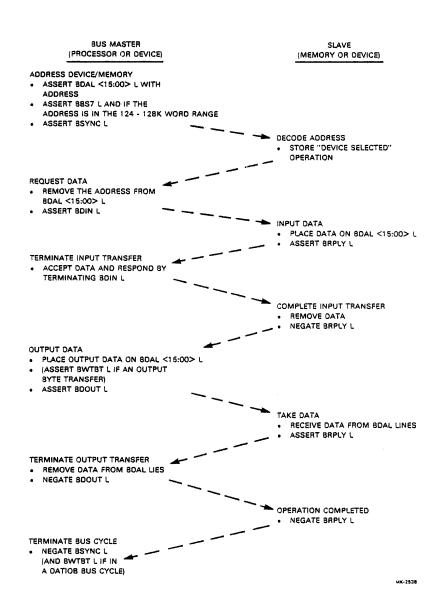

DC010 DIRECT MEMORY ACCESS LOGIC Logic Diagram .......43 Electrical Characteristics......47 Setup Time/Pulse Width Switching Characteristics Table............53 **APPLICATIONS** General......58 HARDWARE FOR CHIPKITS APPENDIX LSI-11 Bus Timings.......87

#### ORDERING INFORMATION

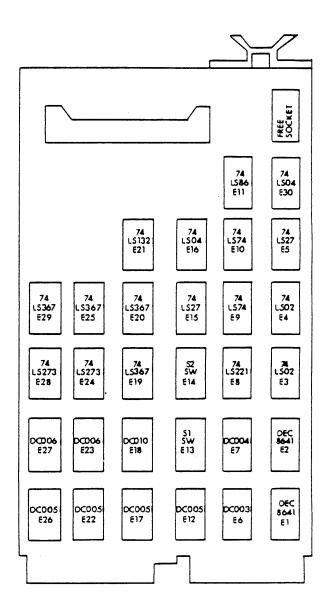

Chipkits are designed to provide the design engineer with the material necessary to prototype a new LSI-11 Bus interface. Each kit provides the DEC chips used to implement either a program control (PC) or direct memory access (DMA) interface. The DCK11-AC and DCK11-AD chipkits also provide the W9512 wire wrappable module and interface cable.

LSI-11 Bus Interface chips are sold in several packages depending upon the customer application. A chipkit, as implemented in your custom design, will consist of a combination of up to five different types of DEC-supplied integrated circuits. During your prototyping process you may choose from four types of chipkits. It is often easier to construct initial designs using the chipkits than to build directly from chips. Later, when your design goes into volume production, you may save money by implementing the design with individual chips, rather than with the chipkits.

Except where noted, these products are available from the Technical Volume Group of Digital Equipment Corporation and authorized industrial distributors.

The following table describes the chipkits:

|              |      |       |       | Com   | ponents |       |                                       |

|--------------|------|-------|-------|-------|---------|-------|---------------------------------------|

| Model Number | Type | DC003 | DC004 | DC005 | DC006   | DC010 | W9512                                 |

| DCKA11-AA    | PC   | 1     | 1     | 4     |         |       |                                       |

| DCK11-AB     | DMA  | 1     | 1     | 4     | 2       | 1     | e e e e e e e e e e e e e e e e e e e |

| DCK11-AC*    | PC   | 1     | 1     | 4     |         |       | , 1                                   |

| DCK11-AD*    | DMA  | 1     | 1     | 4     | 2       | 1     | 1                                     |

<sup>\*</sup>These kits are available from DIGITAL's Accessories and Supplies Group only.

The individual chip types used in the chipkits can also be purchased in tubes of 18 chips. When purchased this way, volume discounts apply. These discounts significantly reduce the price of production quantities.

The following table lists the chips and their functions:

| Model Number | Function                                       |

|--------------|------------------------------------------------|

| DC003-KA     | Interrupt chip                                 |

| DC004-KA     | Protocol chip                                  |

| DC005-KA     | Transceiver/address decoder/vector select chip |

| DC006-KA     | Word count/bus address chip                    |

| DC010-KA     | DMA control chips                              |

### INTRODUCTION

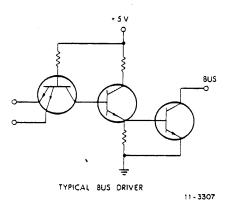

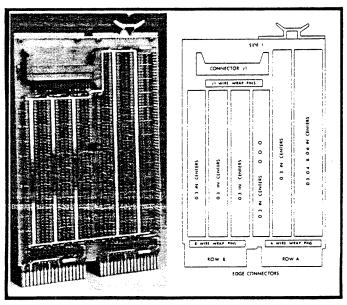

This Users Manual contains descriptions, specifications, and circuit diagrams for the five integrated circuits available in CHIPKITS for use in LSI-11 bus interfaces. The bus receiver and bus driver chips usually used with the LSI-11 are also covered, and the W9512 wire wrappable module included with the designers kits is described.

DCK11-AC and AD CHIPKITS include LSI IC chips, a wire wrappable board, and an interface cable.

The DCK11 series of proprietary LSI integrated circuits, developed by DIGITAL for its own use, is now available to LSI-11 users. These ICs, available in sets called CHIPKITS, make design of LSI-11 bus interfaces easier than ever. The kits contain the ICs needed to build the foundation of nearly any LSI-11 interface, and are available either with or without a DIGITAL wire wrappable board and plug-in cable.

The CHIPKITS minimize the chip count required to implement bus circuitry. This permits the designer to build an interface foundation on the double-height wire wrappable board provided, and still have ample room left for his special circuitry. The comparatively small chip count results in backplane space savings, increased system reliability, lower system cost, and a greater opportunity for value to be added by the CHIPKIT customer to the finished product.

The CHIPKITS in this program are:

DCK11-AC Designers Program Control Bus Interface CHIPKIT, consisting

- 1 DC003 Interrupt Chip

- 1 DC004 Protocol Chip

- 4 DC005 Transceiver/Address Decoder/Vector Select Chips

- 1 W9512 Double-height, extended-length, wire wrappable module

- 1 BC07D-10 ten-foot, 40-conductor plug-in cable

DCK11-AA Program Control Bus Interface CHIPKIT, consisting of the six chips of the above DCK11-AC, but no module or cable.

These kits are ideal for building the foundations of program control bus interfaces to the LSI-11. They are functionally similar to DIGITAL's DRV11-P Bus Foundation Module, an assembled, ready-to-use option.

DCK11-AD Designers DMA Bus Interface CHIPKIT, consisting of:

- DC003 Interrupt Chip

- DC004 Protocol Chip

- 4 DC005 Transceiver/Address Decoder/Vector Select Chips

- 2 DC006 Word Count/Bus Address Chips

- DC010 DMA Control Chip

- 1 W9512 Double-height, extended-length, wire wrappable module

- BC07D-10 ten-foot, 40-conductor plug-in cable

DCK11-AB DMA Bus Interface CHIPKIT, consisting of the nine chips of the above DCK11-AD, but no module or cable.

These kits are ideal for building the foundations of DMA bus interfaces to the LSI-11. They are functionally similar to DIGITAL's DRV11 B General Purpose DMA Interface Module.

## **Brief Specifications of CHIPKIT Integrated Circuits**

## **Absolute Maximum Ratings:**

Supply Voltage (Vcc) +7V Input Voltage (VI) +5.5V

Operating Temp. (Ta) +32°F to +158°F (0°C to +70°C)

Storage Temp. (Ts) +32°F to +302°F (-65°C to +150°C)

# **Recommended Operating Conditions:**

Supply Voltage (Vcc) 4.75V (Min.) 5.0V (Norm), 5.25V (Max)

Supply Current (Vcc) DC003: 140 mA (Max)

DC004, DC005: 120 mA (Max) DC006: 170 mA (Max) DC010: 160 mA (Max)

Free Air Temperature

Relative Humidity

+32°F to +158°F (0°C to +70°C) 10% to 95%, non-condensing

# Physical Dimensions:

DC003, 18-pin

0.3" center

DEC 19-12730-00

DC004, 20-pin

0.3" center

DEC 19-12729-00

DC005, 20-pin

0.3" center

DEC 19-13040-00

DC006, 20-pin

0.3" center

DEC 19-14035-00

DC010, 20-pin

0.3" center

DEC 19-14038-00

W9512 Wire

Double height, extended length, single width.

Wrappable Module

BC07D-10 Cable

10', 40-conductor ribbon cable, with 40-pin (female) mating connector (H856) installed on one end only;

prestripped on other end.

Detailed specifications, circuit diagrams, pin/signal descriptions, and timing diagrams for each IC follow in this Users Manual.

# DC003 Interrupt Logic (DEC #19-12730-00)

The interrupt chip is an 18-pin, 0.762 cm center  $\times$  2.349 cm long (max) (0.3 in center  $\times$  0.925 in long) dual-in-line-package (DIP) device that provides the circuits to perform an interrupt transaction in a computer system that uses a daisy-chain type of arbitration scheme. The device is used in peripheral interfaces to provide two interrupt channels labeled "A" and "B," with the A section at a higher priority than the B section. Bus signals use high-impedance input circuits or high current open-collector outputs, which allow the device to directly attach to the computer system bus. Maximum current required from the  $V_{CC}$  supply is 140 mA.

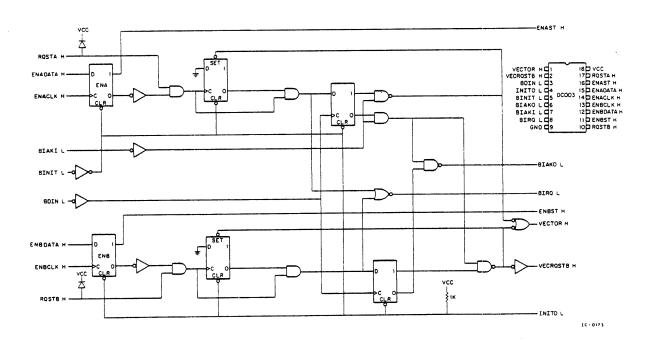

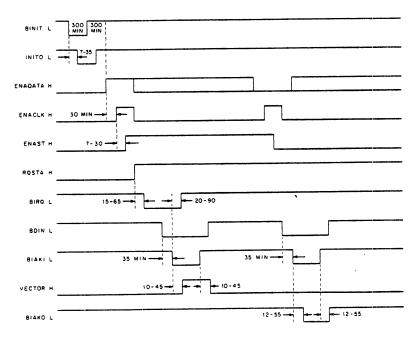

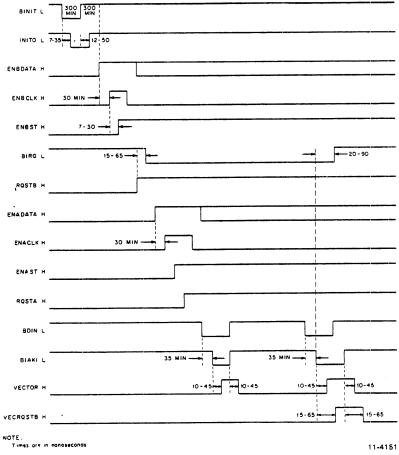

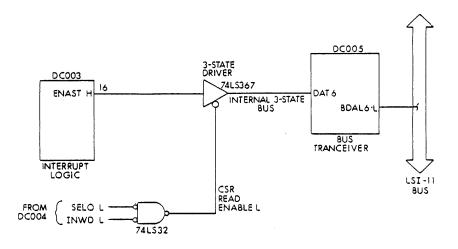

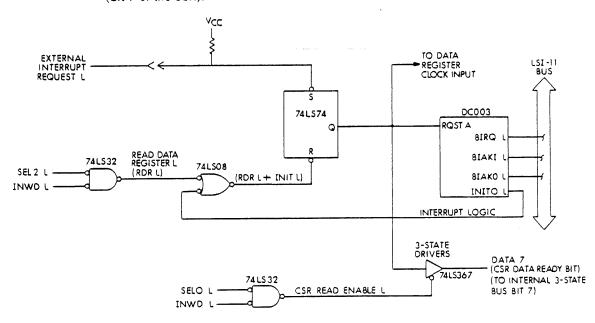

Figure 1 is a simplified logic diagram of the DC003 IC. Figure 2 shows the test conditions used to derive the data presented in the Electrical Characteristics. Figure 3 shows the timing for the "A" interrupt section while Figure 4 shows the timing for both "A" and "B" interrupt sections. Table 1 describes the signals and pins of the DC003 by pin and signal name.

Figure 1 DC003 Simplified Logic Diagram

Table 1 DC003 Pin/Signal Descriptions

| Pin | Signal     | Spec<br>Group | Description                                                                                                                                                                                                                                                                                                                                                               |

|-----|------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

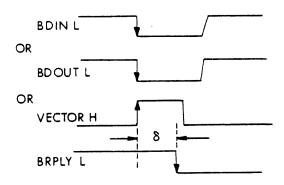

| 1   | VECTOR H   | l             | Interrupt Vector Gating. This signal should be used to gate the appropriate vector address onto the bus and to form the bus signal called BRPLY L.                                                                                                                                                                                                                        |

| 2   | VECRQSTB H | l             | Vector Request "B." When asserted, indicates RQST "B" service vector address is required. When unasserted, indicates RQST "A" service vector address is required. VECTOR H is the gating signal for the entire vector address; VECRQSTBH is normally bit 2 of the vector address.                                                                                         |

| 3   | BDIN L     | 111           | Bus Data In. This signal, generated by the processor BDIN, always precedes a BIAK signal.                                                                                                                                                                                                                                                                                 |

| 4   | INITO L    | j*            | Initialize Out. This is the buffered BINIT L signal used in the device interface for general initialization.                                                                                                                                                                                                                                                              |

| 5   | BINIT L    | 111           | Bus Initialize. When asserted, this signal brings all driven lines to their unasserted state (except INITO L).                                                                                                                                                                                                                                                            |

| 6   | BIAKO L    | 11            | Bus Interrupt Acknowledge (Out). This signal is the daisy-chained signal that is passed by all devices not requesting interrupt service (see BIAKI L). Once passed by a device, it must remain passed until a new BIAKI L is generated.                                                                                                                                   |

| 7   | BIAKI L    | 111           | Bus Interrupt Acknowledge (In). This signal is the processor's response to BIRQ L true. This signal is daisy-chained such that the first requesting device blocks the signal propagation while non-requesting devices pass the signal on as BIAKO L to the next device in the chain. The leading edge of BIAKI L causes BIRQ L to be unasserted by the requesting device. |

<sup>\*</sup>Open collector with 1 K ohm pullup resistor

Table I DC003 Pin/Signal Descriptions (Cont)

| Pin      |                        | oup        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8        | BIRQ L                 | II         | Bus Interrupt Request. This signal is generated when this device needs to interrupt the processor. The request is generated by a false to true transition of the RQST signal along with the associated true interrupt enable signal. The request is removed after the acceptance of the BDIN L signal and on the leading edge of the BIAKI L signal or the removal of the associated interrupt enable or the removal of the associated request signal. |

| 10<br>17 | RQSTB H<br>RQSTA H     | 111<br>111 | Device Interrupt Request. When asserted with the enable flip-flop set, will cause the assertion of BIRQ L on the bus. This signal line normally remains asserted until the request is serviced.                                                                                                                                                                                                                                                        |

| 11<br>16 | ENBST H<br>ENAST H     | !          | Interrupt Enable Status. This signal indicates the state of the interrupt enable internal flip-flop which is controlled by the signal ENX (where X is either A or B) DATA H and the ENX (where X is either A or B) CLK H clock line.                                                                                                                                                                                                                   |

| 12<br>15 | ENBDATA H<br>ENADATA H | I          | interrupt Enable Data. The level on this line, in conjunction with the ENX (where X is either A or B) CLK H signal, determines the state of the internal interrupt enable flip-flop. The output of this flip-flop is monitored by the ENX (where X is either A or B) ST H signal                                                                                                                                                                       |

| 13<br>14 | ENBCLK H<br>ENACLK H   | 1          | Interrupt Enable Clock. When asserted (on<br>the positive edge), interrupt enable flip-<br>flop assumes the state of the ENX (where<br>X is either A or B) DATA H signal line.                                                                                                                                                                                                                                                                         |

# **Specifications**

# DC003 Electrical Characteristics

# DC003 TTL (Non-Bus) Interface (Specification Group I – TTL Input and Output Pins)

| Parameter                               |                 |                                                                               |                 | Requireme | nts  |

|-----------------------------------------|-----------------|-------------------------------------------------------------------------------|-----------------|-----------|------|

| Name                                    | Symbol          | Conditions*                                                                   | Min             | Max       | Unit |

| High-level input voltage                | Vін             | (See Fig. 2A, 2B)                                                             | 2.0             |           | ٧    |

| Low-level input voltage                 | VIL             | (See Fig. 2A, 2B)                                                             |                 | 0.8       | ٧    |

| input clamp voit-<br>age                | Vı              | $V_{cc} = 4.75 \text{ V}$<br>$I_1 = -18 \text{ mA}$<br>(See Fig. 2C)          |                 | -1.2      | ٧    |

| High-level output<br>voltage            | V <sub>он</sub> | $V_{cc} = 4.75 \text{ V}$ $I_0 = -1 \text{ mA}$ (See Fig. 2A)                 | 2.7             |           | ٧    |

| Low-level output voltage                | Vol             | $V_{cc} = 4.75 \text{ V}$<br>$I_0 = 20 \text{ mA}$<br>(See Fig. 2B)           |                 | 0.5       | ٧    |

| Input current: at maximum input voltage | I <sub>E</sub>  | $V_{cc} = 5.25 \text{ V}$<br>$V_1 = 5.5 \text{ V}$<br>(See Fig. 2D)           |                 | 1         | mA   |

| High-level input current                | Ін              | $V_{cc} = 5.25 \text{ V}$<br>$V_1 = 2.7 \text{ V}^{\dagger}$<br>(See Fig. 2D) |                 | 50        | μΑ   |

| Low-level input current                 | lic.            | $V_{cc} = 5.25 \text{ V}$<br>$V_1 = 0.5 \text{ V}$<br>(See Fig. 2E)           |                 | -0.55     | mA   |

| Short-circuit out-<br>put current       | los             | V∞ = 5.25 V§ (See Fig. 2F)                                                    | <del>-4</del> 0 | -100      | mA   |

| Supply current                          | lce             | $V_{cc} = 5.25 \text{ V}$ (See Fig. 2G)                                       |                 | 140       | mA   |

<sup>\*</sup>Ambient operating temperature (Ta) =  $0^{\circ}$  to  $+70^{\circ}$  C unless otherwise specified.

<sup>†</sup> IIH = 100  $\mu$ A at pins 12 and 15.

$<sup>\</sup>ddagger$  liL = -2.0 mA at pins 12 and 15.

<sup>§</sup> Not more than one output shall be shorted at a time and duration shall not exceed 1 second.

Does not apply to pin 4.

DC003 Bus Driver (Specification Group II – Open Collector)

| Parameter                   | Requirements |                                                                                                    |     |            |        |

|-----------------------------|--------------|----------------------------------------------------------------------------------------------------|-----|------------|--------|

| Name                        | Symbol       | Conditions <sup>1</sup>                                                                            | Min | Max        | Unit   |

| Output reverse<br>current   | los          | $V_{CC} = 4.75 \text{ V}$<br>$V_{OH} = 3.5 \text{ V}$<br>(See Fig. 2A)                             |     | 25         | μΑ     |

| Low-level output<br>voltage | Vol          | V <sub>cc</sub> =4.75 V<br>I <sub>SINK</sub> = 70 mA<br>I <sub>SINK</sub> = 16 mA<br>(See Fig. 2B) |     | 0.8<br>0.5 | V<br>V |

<sup>&</sup>lt;sup>1</sup>Ambient operating temperature  $(T_A) = 0^\circ$  to  $+70^\circ$  C unless otherwise specified.

DC003 Bus Receiver (Specification Group III - High Input Z)

| Parameters               |        |                                                                                                                                 | R            | equireme     | erits                    |

|--------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------------------|

| Name                     | Symbol | Conditions <sup>1</sup>                                                                                                         | Min          | Max          | Unit                     |

| High-level input voltage | ViH    | $V_{cc} = 4.75 \text{ V}$<br>$V_{cc} = 5.25 \text{ V}$<br>(See Fig. 2A, 2B)                                                     | 1.53<br>1.70 |              | V<br>V                   |

| Low-level input voltage  | VIL    | $V_{cc} = 4.75 \text{ V}$<br>$V_{cc} = 5.25 \text{ V}$<br>(See Fig. 2A, 2B)                                                     |              | 1.30<br>1.47 | <b>V</b>                 |

| input ciamp<br>voltage   | Vi     | $V_{cc}=4.75 \text{ V}$<br>$I_1=-18 \text{ mA}$<br>$I_1=+18 \text{ mA}$<br>(pins 10 and 17 only)<br>(See Fig. 2C)               |              | -1.2<br>6.25 | v<br>v                   |

| High-level input current | liн    | $V_1 = 3.8 \text{ V}$<br>$V_{cc} = 0.\text{ V}$<br>(Do not do for pins 10 and 17)<br>$V_{cc} = 5.25 \text{ V}$<br>(See Fig. 2D) |              | 40<br>40     | μ <b>Α</b>               |

| Low-level input current  | lπ     | $V_1 = 0 \text{ V}$<br>$V_{cc} = 0 \text{ V}$<br>(Do not do for pins 10 and 17)<br>$V_{cc} = 5.25 \text{ V}$<br>(See Fig. 2E)   |              | -10<br>-10   | μ <b>Α</b><br>μ <b>Α</b> |

<sup>&</sup>lt;sup>1</sup>Ambient operating temperature  $(T_A) = 0^\circ$  to  $+70^\circ$  C unless otherwise specified.

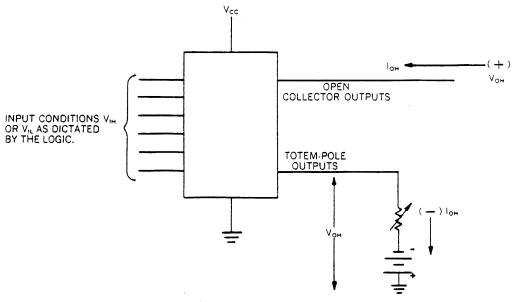

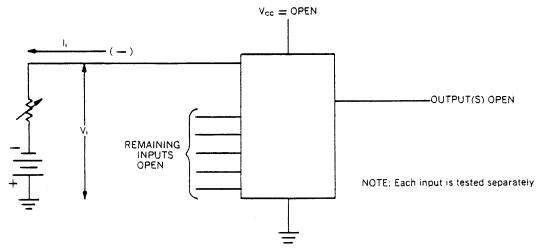

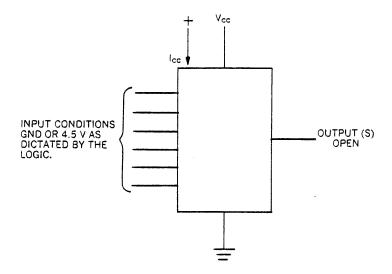

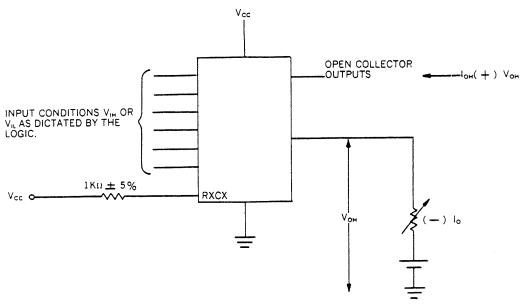

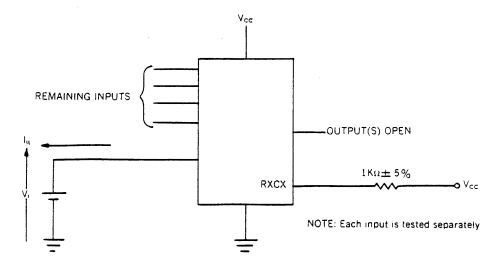

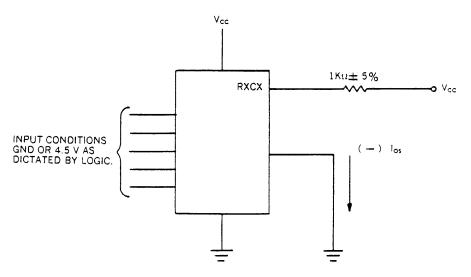

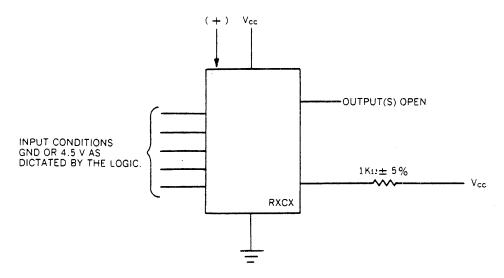

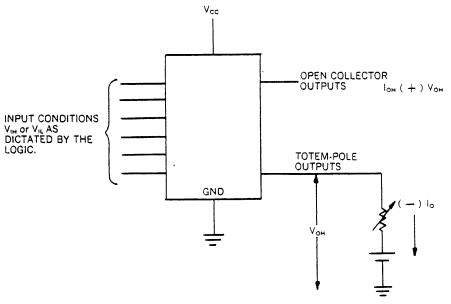

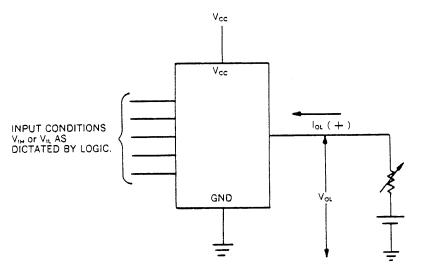

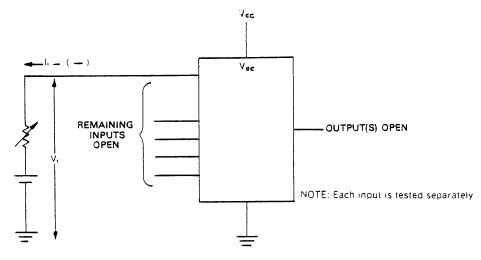

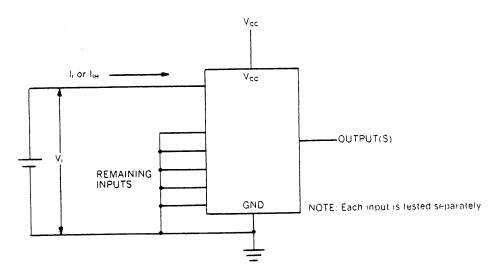

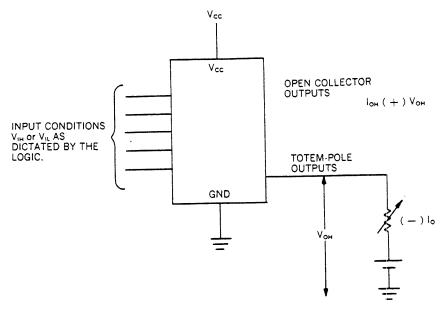

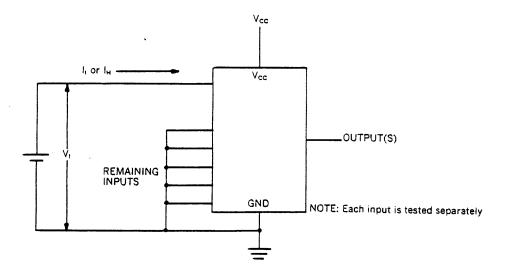

Figure 2A — DC Test Circuit ( $V_{IH}$ ,  $V_{IL}$ ,  $V_{OH}$ ,  $I_{OH}$ )

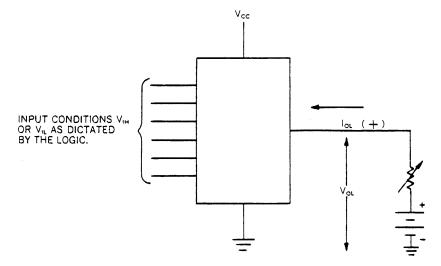

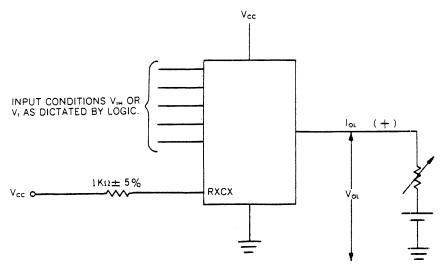

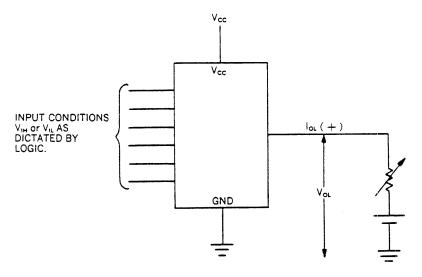

Figure 2B — DC Test Circuit (VIH, VIL, Vol.)

Figure 2C - DC Test Circuit (Vi)

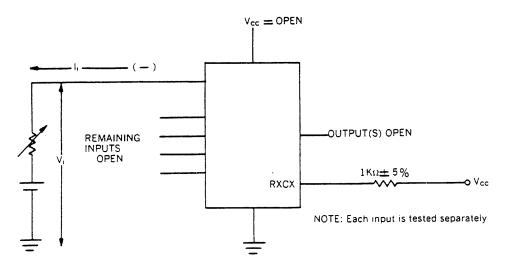

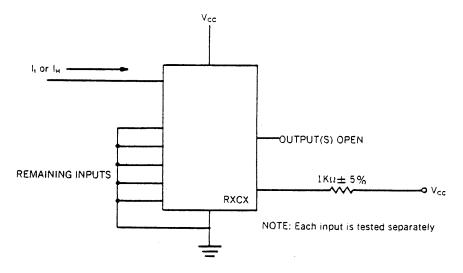

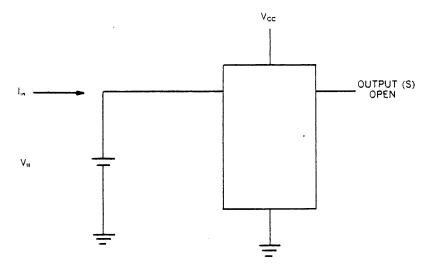

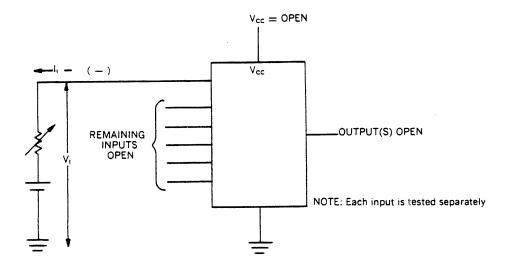

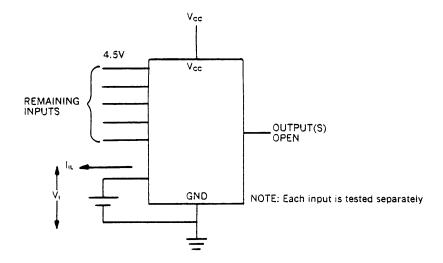

Figure 2D — DC Test Circuit (I, I $_{\mbox{\scriptsize IM}})$

Figure 2E — DC Test Circuit (In)

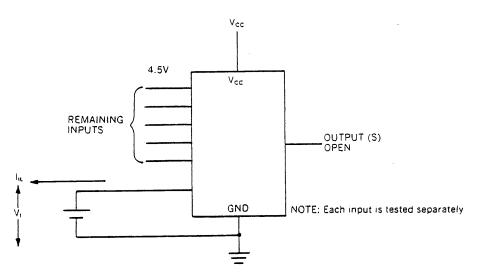

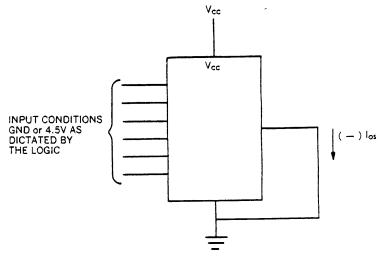

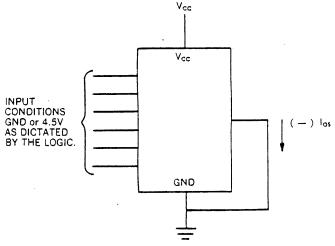

Figure 2F — DC Test Circuit (los)

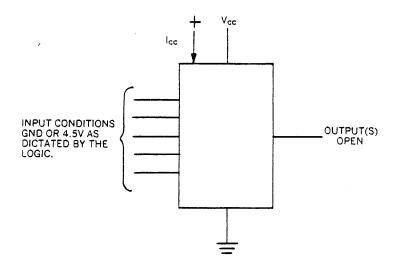

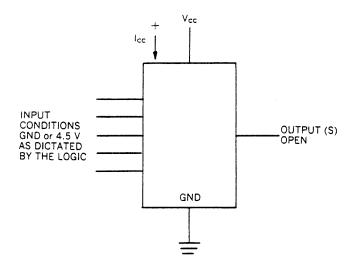

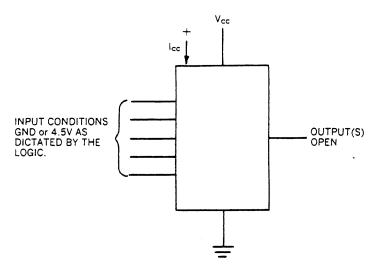

Figure 2G — DC Test Circuit (Icc)

Figure 3 DC003 "A" Interrupt Section Timing Diagram

Figure 4 DC003 "A" and "B" Interrupt Sections Timing Diagrams

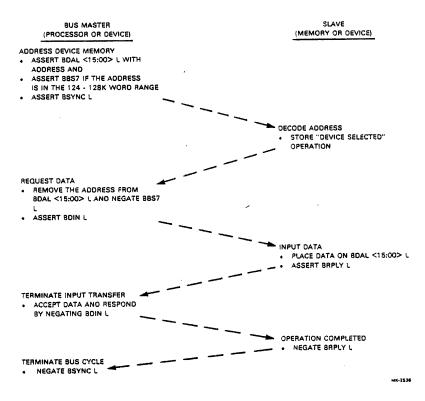

# DC004 PROTOCOL LOGIC (DEC #19-12729-00)

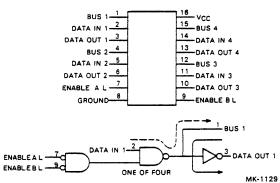

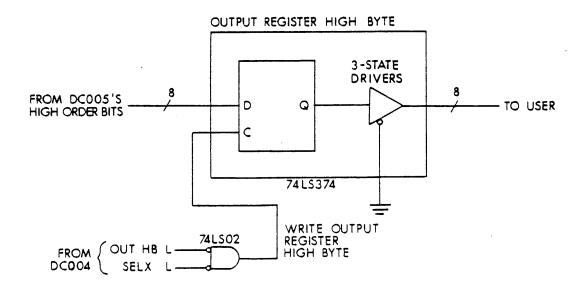

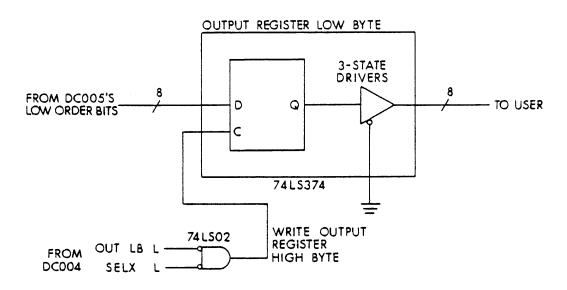

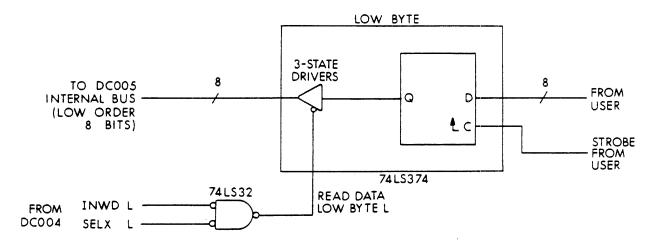

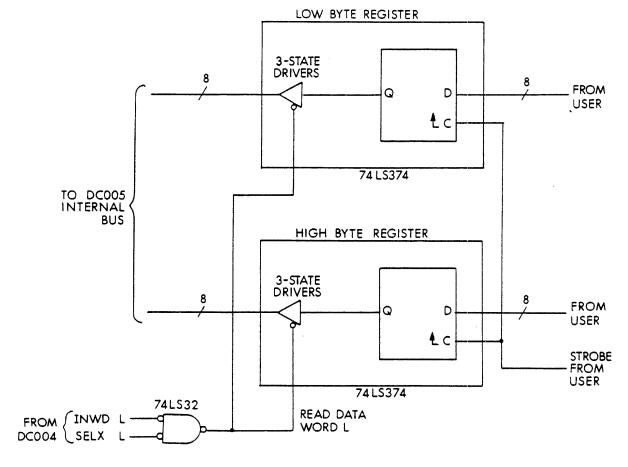

The protocol chip is in a 20-pin 0.762 cm center X 2.74 cm long (0.3 in center X 1.08 in long) DIP device that functions as a register selector, providing the signals to control data flow into and out of up to four word registers (eight bytes). Bus signals can directly attach to the device because receivers and drivers are provided on the chip. An RC delay circuit is provided to slow the response of the peripheral interface to data transfer requests. The circuit is designed such that if tight tolerance is not required, then only an external 1 K  $\pm$  20 percent resistor is necessary. External RCs can be added to vary the delay (see Table 3). Maximum current required from the Vcc supply is 120mA.

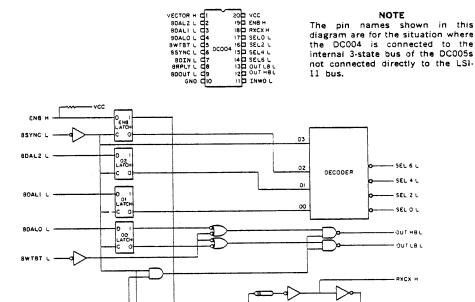

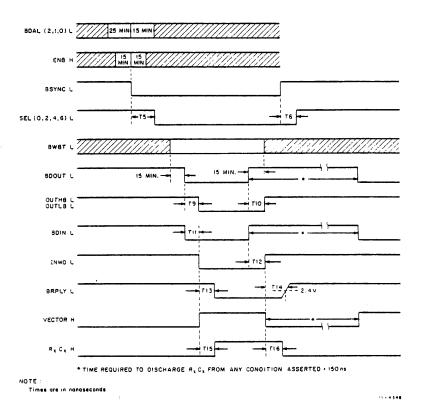

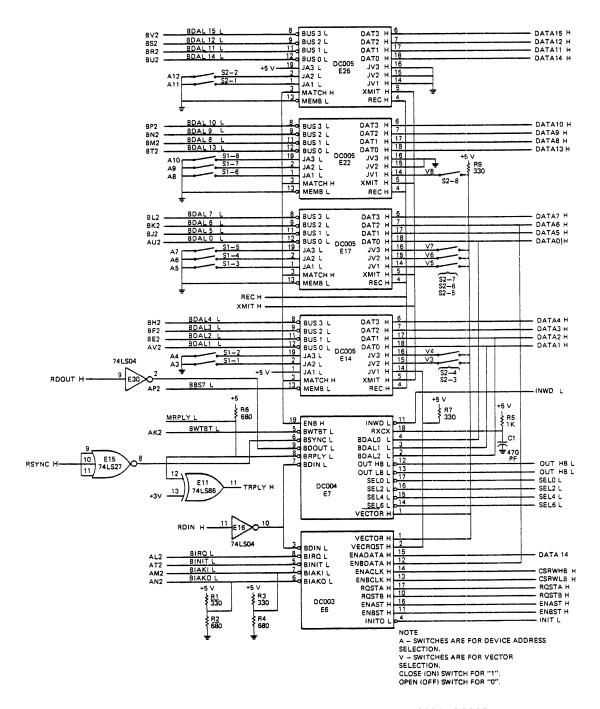

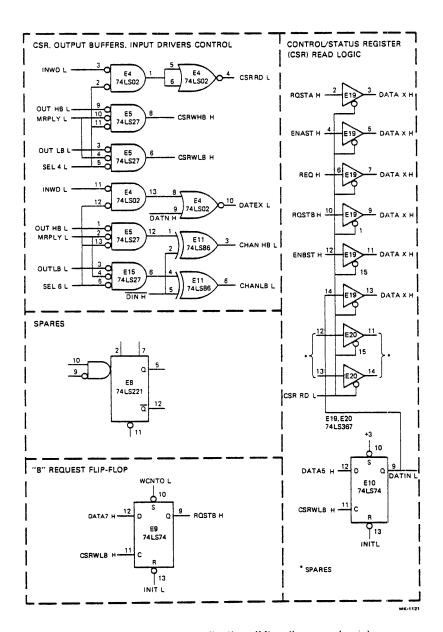

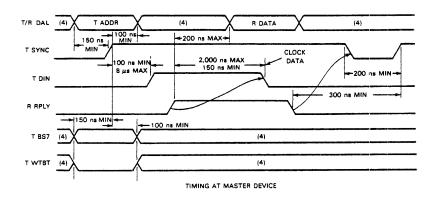

Figure 5 is a simplified logic diagram of the DC004 IC. Signal timing with respect to different loads is shown in Table 3 and in Figure 7. Figure 6 shows the test conditions used while Figure 8 shows the loading for the test conditions. Signal and  $\rho$ m definitions for the DC004 are presented in Table 2.

Figure 5 DC004 Simplified Logic Diagram

ENWO L

Table 2 DC004 Pin/Signal Descriptions

| Pin         | Signal                        | Spec<br>Group  | Description                                                                                                                                                                                                      |

|-------------|-------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | VECTOR H                      | l              | Vector. This input causes BRPLY L to be generated through the delay circuit. Independent of BSYNC L and ENB H.                                                                                                   |

| 2<br>3<br>4 | BDAL2 L<br>BDAL1 L<br>BDAL0 L | 11<br>11<br>11 | Bus Data Address Lines. These signals are latched at the assert edge of BSYNC L. Lines 2 and 1 are decoded for the select outputs; line 0 is used for byte selection.                                            |

|             | BWTBT L                       | H              | Bus Write/Byte. While the BDOUT L input is asserted, this signal indicates a byte or word operation: Asserted = byte, unasserted = word. Decoded with BDOUT L and latched BDALO L to form OUT LB L and OUT HB L. |

| 6           | BSYNC L                       | 11             | Bus Synchronize. At the assert edge of this signal, address information is trapped in four latches. While unasserted, disables all outputs except the vector term of BRPLY L.                                    |

| 7           | BDIN L                        | 11 ,           | Bus Data In. This is a strobing signal to effect a data input transaction. Generates BRPLY L through the delay circuit and INWD L                                                                                |

| 8           | BRPLY L                       | Ш              | Bus. Reply. This signal is generated through<br>an RC delay by VECTOR H OR'd with<br>BDIN L or BDOUT L and the AND of<br>BSYNC L and latched ENB H.                                                              |

| 9           | BDOUT L                       | 11             | Bus Data Out. This is a strobing signal to effect a data output transaction. Decoded with BWTBT L and BDALO to form OUT LB L and OUT HB L. Generates BRPLY L through the delay circuit.                          |

| 11          | INWD L                        | t              | in Word. Used to gate (read) data from a selected register onto the data bus. Enabled by BSYNC L and strobed by BDIN L.                                                                                          |

| 12<br>13    | OUT LB L<br>OUT HB L          | 1              | Out Low Byte, Out High Byte. Used to load (write) data into the lower, higher, or both bytes of a selected register. Enabled by BSYNC L and decode of BWTBT L and latched BDALO L, and strobed by BDOUT L.       |

Table 2 DC004 Pin/Signal Descriptions (Cont)

| Pin                  | Signal                               | Spec<br>Group | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------|--------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14<br>15<br>16<br>17 | SELO L<br>SEL2 L<br>SEL4 L<br>SEL6 L | <br>          | Select Lines. One of these four signals is true as a function of BDAL2 L and BDAL1 L if ENB H is asserted at the assert edge of BSYNC L. They indicate that a word register has been selected for a data transaction. These signals never become asserted except at the assertion of BSYNC L (then only if ENB H is asserted at that time) and once asserted, are not unasserted until BSYNC L becomes unasserted. |

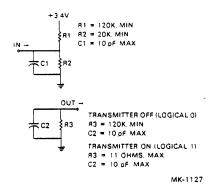

| 18                   | RXCX H                               | 111           | External Resistor Capacitor Node. This node is provided to vary the delay between the BDIN L, BDOUT L, or VECTOR H inputs and BRPLY L output. The external resistor should be tied to Vcc and the capacitor to ground. As an output, it is the logical inversion of BRPLY L.                                                                                                                                       |

| 19                   | ENB H                                | *             | Enable. This signal is latched at the asserted edge of BSYNC L and is used to enable the select outputs and the address term of BRPLY L.                                                                                                                                                                                                                                                                           |

<sup>\*</sup> TTL input with 850  $\Omega$  pull-up resistor to VCC.

**DC004 Electrical Characteristics**

TTL (Non-Bus) Interface (Specification Group I – TTL Input and Output Pins)

| Parameter                              |                 |                                                                             |                | Requireme     | nts  |

|----------------------------------------|-----------------|-----------------------------------------------------------------------------|----------------|---------------|------|

| Name                                   | Symbol          | Conditions*                                                                 | Min            | Max           | Unit |

| High-level input<br>voltage            | Vін             | (See Fig. 6A, 6B)                                                           | 2.0            |               | ٧    |

| Low-level input<br>voltage             | VIL             | (See Fig. 6A, 6B)                                                           |                | 8.0           | ٧    |

| Input clamp<br>voltage                 | Vı              | $V_{cc} = 4.75 \text{ V}$<br>$I_1 = -18 \text{ mA}$<br>(See Fig. 6C)        |                | -1.2          | ٧    |

| High-level output voltage              | V <sub>OH</sub> | $V_{cc} = 4.75 \text{ V}$<br>$I_0 = -1 \text{ mA}$<br>(See Fig. 6A)         | 2.7            |               | ٧    |

| Low-level output<br>voltage            | Vor             | $V_{cc} = 4.75 \text{ V}$<br>$I_0 = 20 \text{ mA}$<br>(See Fig. 6B)         |                | 0.5           | ٧    |

| Input current at maximum input voltage | l <sub>t</sub>  | $V_{cc} = 5.25 \text{ V}$<br>$V_1 = 5.5 \text{ V}$<br>(See Fig. 6D)         |                | 1             | mA   |

| High-level input<br>current            | Ін              | $V_{cc} = 5.25 \text{ V}$<br>$V_i = 2.7 \text{ V} \dagger$<br>(See Fig. 6D) |                | 50            | μΑ   |

| Low-level input<br>current             | lu.             | $V_{cc} = 5.25 \text{ V}$<br>$V_1 = 0.5 \text{ V}$<br>(See Fig. 6E)         |                | <b>-</b> 0.70 | mA   |

| Short-circuit output current           | los             | Vcc = 5.25 V‡<br>(See Fig. 6F)                                              | <del>4</del> 0 | -100          | mA   |

| Supply current                         | lcc             | $V_{cc} = 5.25 \text{ V}$ (See Fig. 6G)                                     |                | 120           | mA   |

<sup>\*</sup>Ambient operating temperature (Ta) =  $0^{\circ}$  to  $+70^{\circ}$  C unless otherwise specified.

<sup>†</sup>Limits for pin 19 are:

$l_1 = 1.40$  mA;  $l_1H = -2.25$  mA min, -3.85 mA max.

lil = -4.5 mA min, -8.0 mA max.

<sup>‡</sup> Not more than one output shall be shorted at a time and the duration shall not exceed 1 second.

DC004 Bus Receiver (Specification Group II - High Input Z)

| Parameter                   |        |                                                                                               | R            | equirem      | ents                     |

|-----------------------------|--------|-----------------------------------------------------------------------------------------------|--------------|--------------|--------------------------|

| Name                        | Symbol | Conditions*                                                                                   | Min          | Max          | Unit                     |

| High-level input<br>voltage | Vie    | $V_{cc} = 4.75 \text{ V}$<br>$V_{cc} = 5.25 \text{ V}$<br>(See Fig. 6A, 6B)                   | 1.53<br>1.70 |              | V<br>V                   |

| Low-level input<br>voltage  | VIL    | $V_{cc} = 4.75 \text{ V}$<br>$V_{cc} = 5.25 \text{ V}$<br>(See Fig. 6A, 6B)                   |              | 1.30<br>1.47 | <b>V V</b>               |

| Input clamp<br>voltage      | Vı     | $V_{cc} = 4.75 \text{ V}$<br>$I_1 = -18 \text{ mA}$<br>(See Fig. 6C)                          |              | -1.2         | ٧                        |

| High-level input<br>current | Ін     | $V_1 = 3.8 \text{ V}$<br>$V_{cc} = 0 \text{ V}$<br>$V_{cc} = 5.25 \text{ V}$<br>(See Fig. 6D) |              | 40<br>40     | μ <b>Α</b><br>μ <b>Α</b> |

| Low-level input current     | ln.    | $V_1 = 0V$<br>$V_{cc} = 0 V$<br>$V_{cc} = 5.25 V$<br>(See Fig. 6E)                            |              | -10<br>-10   | μ <b>Α</b><br>μ <b>Α</b> |

<sup>\*</sup>Ambient operating temperature (TA) =  $0^{\circ}$  to  $+70^{\circ}$  C unless otherwise specified.

DC004 Bus Driver (Specification Group III - Open Collector)

| Parameter                   |        |                                                                                                 | Requirements |                   |              |

|-----------------------------|--------|-------------------------------------------------------------------------------------------------|--------------|-------------------|--------------|

| Name                        | Symbol | Conditions*                                                                                     | Min          | Max               | Unit         |

| Output reverse current      | Іон    | $V_{CC} = 4.75 \text{ V}$<br>$V_{OH} = 3.5 \text{ V}$<br>(See Fig. 6A)                          |              | 25†               | μА           |

| Low-level output<br>voltage | Vor    | V <sub>cc</sub> = 4.75 V<br>Isink = 70 mA‡<br>Isink = 16 mA‡<br>Isink = 15 mA§<br>(See Fig. 6B) |              | 0.8<br>0.5<br>0.5 | <b>V V V</b> |

<sup>\*</sup>Ambient operating temperature (TA) =  $0^{\circ}$  to  $70^{\circ}$  C unless otherwise specified. †65  $\mu$ A for pin 18 (RXCX H).

<sup>‡</sup>Applies to Pin 8 (BRPLY L) only. §Applies to Pin 18 (RXCX H) only.

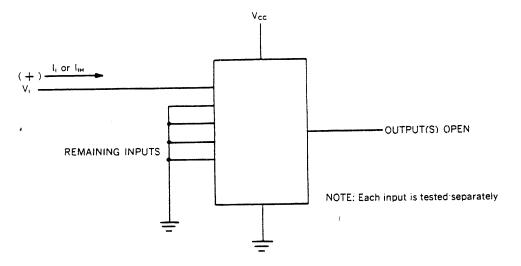

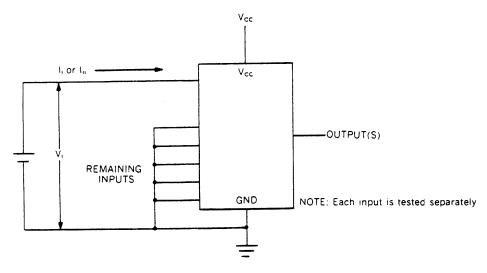

Figure 6A DC Test Circuit (VIH. VIL VOH. IOH)

Figure 6B DC Test Circuit (VIH, VIL, VoL)

Figure 6C DC Test Circuit (Vi)

Figure 6D DC Test Circuit (II, IIH)

Figure 6E DC Test Circuit (IIL)

Figure 6F DC Test Circuit (los)

Figure 6G DC Test Circuit (Icc)

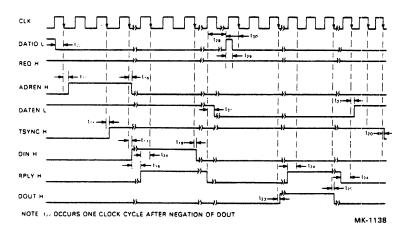

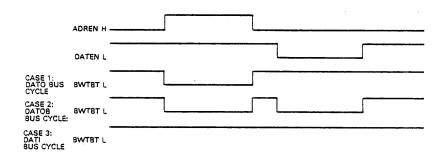

Figure 7 DC004 Timing Diagram

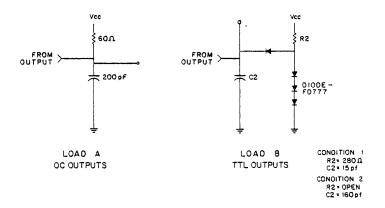

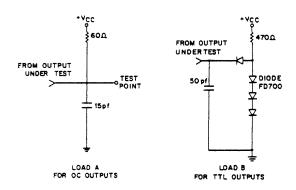

Figure 8 DC004 Loading Configurations for Table 3

Table 3 DC004 Signal Timing vs Output Loading

|                                                   | Signal                 | With<br>Respect<br>to | Signal               | Condi-<br>tion |     | t Being<br>ed (ns)<br>Max |     | ut Being<br>ted (ns)<br>Max | Fig. 5<br>Reference |

|---------------------------------------------------|------------------------|-----------------------|----------------------|----------------|-----|---------------------------|-----|-----------------------------|---------------------|

|                                                   | SEL (0.2,4<br>(Load B) | ,6) L                 | BSYNC L              | 2              | 15  | 40                        | 5   | 30                          | T5, T6              |

|                                                   | OUT LB L               |                       | BDOUT L              | 2              | 5   | 30                        | 5   | 30                          | T9, T10             |

|                                                   | OUT HB L<br>(Load B)   |                       | BDOUT L              | 2              | 5   | 30                        | 5   | 30                          | T9, T10             |

|                                                   | (Load B)               |                       | BDIN L               | 2              | 5   | 30                        | 5   | 30                          | T11, T12            |

| Pin 18<br>Connection                              | BRPLY L<br>(Load A)    |                       | OUT LB L<br>(Load B) | 1              | 20  | 60                        | -10 | 45                          | T13, T14            |

| $RX = 330 \Omega \pm 5\%$<br>$CX = 15 pF \pm 5\%$ |                        |                       | OUT HB L<br>(Load B) | 1              | 20  | 60                        | -10 | 45                          | T13, T14            |

|                                                   | BRPLY L<br>(Load A)    |                       | INWD L<br>(Load B)   | 1              | 20  | 60                        | -10 | 45                          | T13, T14            |

|                                                   | BRPLY L<br>(Load A)    |                       | VECTOR H             |                | 30  | 70                        | 0   | 45                          | T13, T14            |

| Pin 18<br>Connection                              | BRPLY L<br>(Load A)    |                       | OUT LB L<br>(Load B) | 1              | 300 | 400                       | -10 | 45                          | T13, T14            |

| $RX = 4.64K$ $\pm 1\%$                            | BRPLY L<br>(Load A)    |                       | OUT HB L<br>(Load B) | 1              | 300 | 400                       | -10 | 45                          | T13, T14            |

| $CX = 220 \text{ pF}$ $\pm 1\%$                   | BRPLY L<br>(Load A)    |                       | INWD L<br>(Load B)   | 1              | 300 | 400                       | -10 | 45                          | T13, T14            |

|                                                   | BRPLY L<br>(Load A)    |                       | VECTOR H             |                | 330 | 430                       | 0   | 45                          | T13, T14            |

| Pin 18                                            | RXCX H )               |                       | OUT LB L             |                | 10  | 50                        | 10  | 50                          | T15, T16            |

| Connection                                        | RXCX H                 | (Load                 | OUT HB L             |                | 10  | 50                        | 10  | 50                          | T15, T16            |

| $RX = 330 \Omega$ $\pm 5\%$                       | RXCX H                 | A)                    | INWD L               |                | 10  | 50                        | 10  | 50                          | T15, T16            |

| CX = 15 pF<br>± 5%                                | RXCX H                 |                       | VECTOR H             |                | 10  | 50                        | 10  | 50                          | T15, T16            |

See Figure 8.

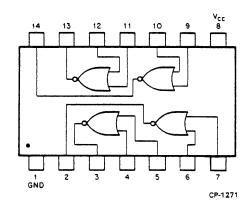

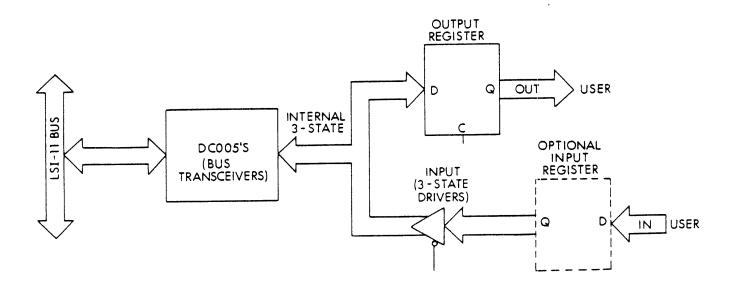

# DC005 TRANSCEIVER LOGIC (DEC # 19-13040-00)

The 4-bit transceiver is a 20-pin, 0.762 cm center X 2.74 cm long (0.3 in. center X 1.08 in. long) DIP, low-power Schottky device; its primary use is in peripheral device interfaces to function as a bidirectional buffer between a data bus and peripheral device logic bus. It also includes a comparison circuit for device address, selection and a constant generator for interrupt vector address generation. The bus I/O port provides high-impedance inputs and high drive (70 mA) open collector outputs to allow direct connection to a computer data bus structure. On the peripheral device side, a bidirectional port is also provided, with standard TTL inputs and 20 mA, tri-state drivers. Data on this port are the logical inversion of the data on the bus side.

Three address "jumper" inputs are used to compare against three bus inputs to generate the signal MATCH. The MATCH output is open collector, which allows the output of several transceivers to be wire-ANDed to form a composite address match signal. The address jumpers can also be put into a third logical state that disables jumpers for "don't care" address bits. In addition to the three address jumper inputs, a fourth high-impedance input line is used to enable/disable the MATCH output.

Three vector jumper inputs are used to generate a constant that can be passed to the computer bus. The three inputs directly drive three of the bus lines, overriding the action of the control lines.

Two control signals are decoded to give three optional states: receive data, transmit data, and disable.

Maximum current required from the VCC supply is 120 mA.

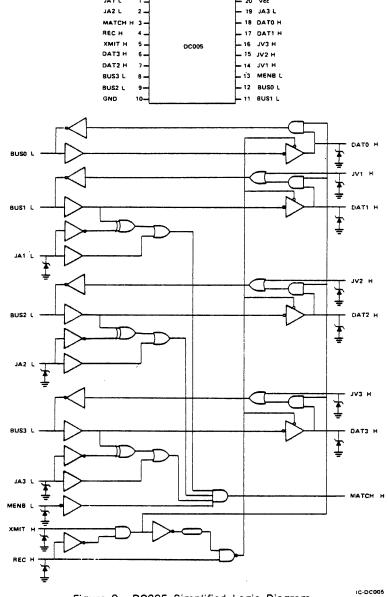

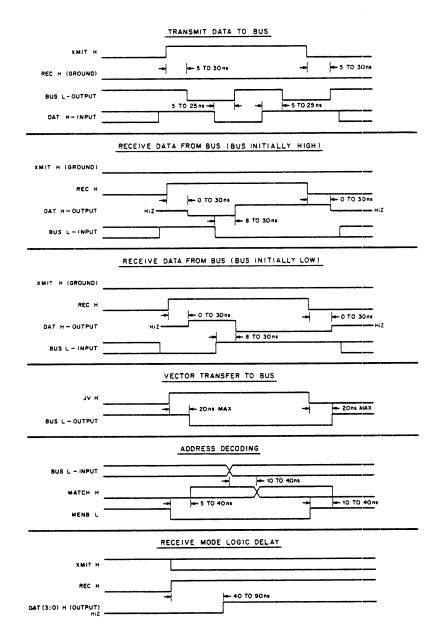

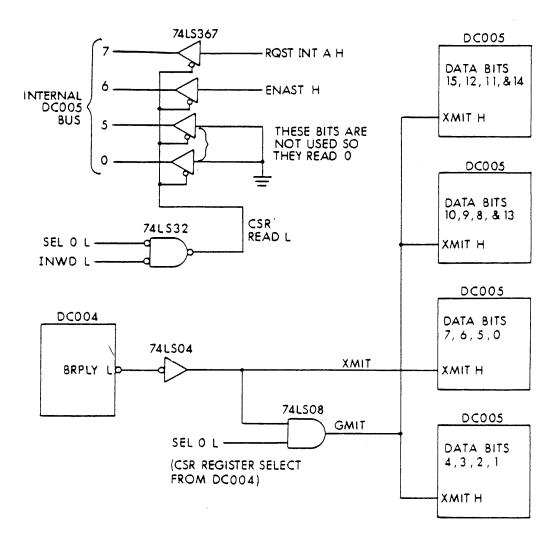

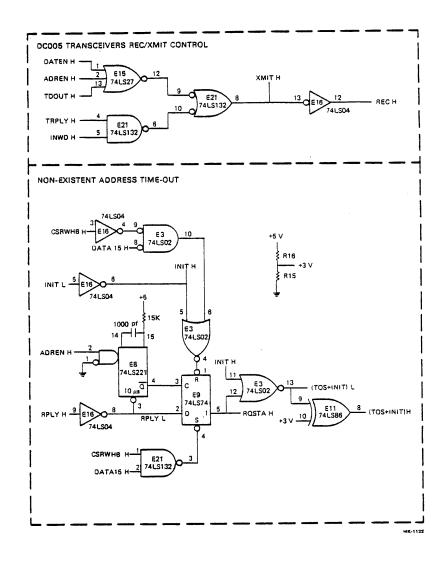

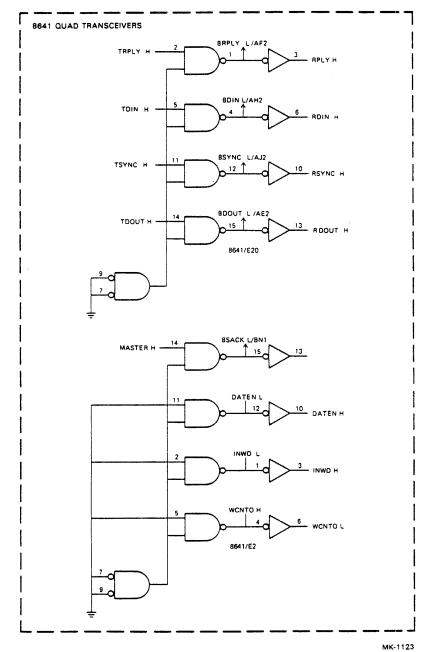

Figure 9 is a simplified logic diagram of the DC005 IC. Timing for the various functions is shown in Figure 11. Signal and pin definitions for the DC005 are presented in Table 4. Figure 10 shows the test conditions used to derive the data listed in the Electrical Characteristics.

Figure 9 DC005 Simplified Logic Diagram

Table 4 DC005 Pin/Signal Descriptions

| Pin | Signal     | Spec<br>Group | Description                                                                                                                                                                     |

|-----|------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | BUS(3:0) L |               |                                                                                                                                                                                 |

| 12  | BUSO L     | 11 + 111      | Bus Data. This set of four lines constitutes                                                                                                                                    |

| 11  | BUS1 L     | 11 + 111      | the bus side of the transceiver. Open col-                                                                                                                                      |

| 9   | BUS2 L     | +             | lector outputs; high-impedance inputs.                                                                                                                                          |

| 8   | BUS3 L     | 0 + 0         | Low = 1.                                                                                                                                                                        |

|     | DAT(3:0) H |               |                                                                                                                                                                                 |

| 18  | DATO H     | 1             | Peripheral Device Data. These four tri-                                                                                                                                         |

| 17  | DAT1 H     | 1             | state lines carry the inverted received data                                                                                                                                    |

| 7   | DAT2 H     | i             | from BUS (3:0) when the transceiver is in                                                                                                                                       |

| 6   | DAT3 H     | I             | the receive mode. When in transmit data mode, the data carried on these lines is passed inverted to BUS (3:0). When in the disabled mode, these lines go open (HI-Z). High = 1. |

Table 4 DC005 Pin/Signal Descriptions (Cont)

| Pin             | Signal                               | Spec<br>Group    | Description                                                                                                                                                                                                                                                                                                                    |

|-----------------|--------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14<br>15·<br>16 | JV(3:1) H<br>JV1 H<br>JV2 H<br>JV3 H | V<br>V<br>V      | Vector Jumpers. These inputs, with internal pull-down resistors, directly drive BUS (3:1). A low or open on the jumper pin will cause an open condition on the corresponding bus pin if XMIT H is low. A high will cause a one (low) to be transmitted on the bus pin. Note that BUSO L is not controlled by any jumper input. |

| 13              | MENB L                               | 11               | Match Enable. A low on this line will enable the Match output. A high will force Match low, overriding the match circuit.                                                                                                                                                                                                      |

| 3               | матсн н                              | III              | Address Match. When BUS (3:1) match with the state of JA (3:1) and MENB L is low, this output is open; otherwise it is low.                                                                                                                                                                                                    |

| 1<br>2<br>19    | JA(3:1) L<br>JA1 L<br>JA2 L<br>JA3 L | IV<br>- IV<br>IV | Address Jumpers. A strap to ground on these inputs will allow a match to occur with a one (low) on the corresponding BUS line; an open will allow a match with a zero (high); a strap to V <sub>CC</sub> will disconnect the corresponding address bit from the comparison.                                                    |

| 5<br>4          | XMIT H<br>REC H                      | 1                | Control Inputs. These lines control the operation of the transceiver as follows.                                                                                                                                                                                                                                               |

|                 |                                      |                  | REC         XMIT           0         0         DISABLE: BUS, DAT open           0         1         XMIT DATA: DAT → BUS           1         0         RECEIVE: BUS → DAT           1         1         RECEIVE: BUS → DAT                                                                                                     |

|                 |                                      |                  | To avoid 3-state signal overlap conditions, an internal circuit delays the change of modes between XMIT DATA and RECEIVE mode and delays 3-state drivers on the DAT lines from enabling. This action is independent of the DISABLE mode.                                                                                       |

# **DC005 Electrical Characteristics**

# DC005 TTL (Non-Bus) Interface (Specification Group I – TTL Input and Output Pins)

| Parameter                                                                 |          |                                                                                     | Re             | equireme     | nts                      |

|---------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------|----------------|--------------|--------------------------|

| Name                                                                      | Symbol   | Conditions*                                                                         | Min            | Max          | Unit                     |

| High-level input voltage                                                  | ViH      | (See Fig. 10A,<br>10B)                                                              | 2              |              | ٧                        |

| Low-level input voltage                                                   | VIL      | (See Fig. 10A,<br>10B)                                                              |                | 0.8          | ٧                        |

| Input clamp voltage                                                       | V,       | $V_{cc} = 4.75 \text{ V}$<br>$I_1 = -18 \text{ mA}$<br>(See Fig. 10C)               |                | -1.2         | V                        |

| High-level output voltage                                                 | Vон      | $V_{cc} = 4.75 \text{ V}$<br>$I_0 = -1 \text{ mA}$<br>(See Fig. 10A)                | 3.65           |              | ٧                        |

| Low-level output voltage                                                  | Vol      | $V_{cc} = 4.75 \text{ V}$<br>$I_0 = 20 \text{ mA}$<br>(See Fig. 10B)                |                | 0.5          | ٧                        |

| Input current at maximum input voltage                                    | Ĭı       | $V_{cc} = 5.25 \text{ V}$<br>$V_i = 5.5 \text{ V}$<br>(See Fig. 10D)                |                | 1            | mA                       |

| High-level input<br>current                                               | Ін       | $V_{cc} = 5.25 \text{ V}$<br>$V_t = 2.7 \text{ V}$<br>REC<br>XMIT<br>(See Fig. 10D) |                | 100<br>50    | μ <b>Α</b><br>μ <b>Α</b> |

| Low-level input current                                                   | I iL     | $V_{cc} = 5.25 \text{ V}$<br>$V_i = 0.5 \text{ V}$<br>REC<br>XMIT<br>(See Fig. 10E) |                | -2.2<br>-1.1 | mA<br>mA                 |

| Short-circuit output current                                              | los      | Vcc = 5.25 V† (See Fig. 10F)                                                        | <del>4</del> 0 | -100         | mA                       |

| Supply current                                                            | lcc      | $V_{cc} = 5.25 \text{ V}$ (See Fig. 10G)                                            |                | 120          | mA                       |

| Off state (high-<br>impedance state)<br>output current<br>(DAT pins only) | lo (OFF) | $V_{cc} = 5.25 \text{ V}$ $V_1 = 3.65 \text{ V}$ $V_1 = 0.5 \text{ V}$              |                | 100<br>—0.36 | μA<br>mA                 |

<sup>\*</sup>Ambient operating temperature  $(T_A) = 0^\circ$  to  $+70^\circ$  C unless otherwise specified.

$<sup>\</sup>dot{\uparrow}$  Not more than one output shall be shorted at a time and the duration shall not exceed 1 second.

DC005 Bus Receiver (Specification Group II – High Input Z)

| Parameter                                                                          |                 |                                                                                                | R            | equireme     | ents                     |

|------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------|--------------|--------------|--------------------------|

| Name                                                                               | Symbol          | Conditions*                                                                                    | Min          | Max          | Unit                     |

| High-level input voltage                                                           | Vін             | V <sub>cc</sub> = 4.75 V<br>V <sub>cc</sub> = 5.25 V<br>(See Fig. 10A,<br>10B)                 | 1.53<br>1.70 |              | V ·                      |

| Low-level input voltage                                                            | Vil             | $V_{cc} = 4.75 \text{ V}$<br>$V_{cc} = 5.25 \text{ V}$<br>(See Fig. 10A,<br>10B)               |              | 1.30<br>1.47 | <b>V</b>                 |

| Input clamp<br>voitage                                                             | Vı              | $I_1 = -18 \text{ mA}$<br>$V_{cc} = 4.75 \text{ V}$<br>(See Fig. 10C)                          |              | -1.2         | ٧                        |

| High-level input<br>current (includes<br>open-collector<br>leakage on bus<br>pins) | l <sub>im</sub> | $V_1 = 3.8 \text{ V}$                                                                          |              |              |                          |

| MENB                                                                               |                 | $V_{cc} = 0 \text{ V}$<br>$V_{cc} = 5.25 \text{ V}$                                            |              | 40<br>40     | μ <b>Α</b><br>μ <b>Α</b> |

| BUS                                                                                |                 | V <sub>cc</sub> = 0 V<br>V <sub>cc</sub> = 5.25 V<br>(See Fig. 10D)                            |              | 65<br>65     | μΑ<br>μΑ                 |

| Low-level input<br>current                                                         | lı,             | $V_1 = 0.5 \text{ V}$<br>$V_{cc} = 0 \text{ V}$<br>$V_{cc} = 5.25 \text{ V}$<br>(See Fig. 10E) |              | -10<br>-10   | μ <b>Α</b><br>μ <b>Α</b> |

<sup>\*</sup>Ambient operating temperature (T<sub>A</sub>) =  $0^{\circ}$  to  $+70^{\circ}$  C unless otherwise specified.

DC005 Bus Driver (Specification Group III – Open Collector)

| Parameter                                                      |        |                                                                          | F   | Requirem | ents |

|----------------------------------------------------------------|--------|--------------------------------------------------------------------------|-----|----------|------|

| Name                                                           | Symbol | Conditions*                                                              | Min | Max      | Unit |

| High-level output current (reverse current—match output only)† | Іон    | $V_{CC} = 4.75 \text{ V}$<br>$V_{OH} = 5.25 \text{ V}$<br>(See Fig. 10A) |     | 25       | μА   |

| Low-level output voltage                                       | Vor    | $V_{cc} = 4.75 \text{ V}$ $I_{SINK} = 8 \text{ mA}$ (Match)              |     | 0.5      | ٧    |

|                                                                |        | Isink = 70 mA (Bus)                                                      |     | 0.8      | ٧    |

|                                                                |        | Isink = 16 mA<br>(Bus)<br>(See Fig.10B)                                  |     | 0.5      | ٧    |

<sup>\*</sup>Ambient operating temperature (T<sub>A</sub>) =  $0^{\circ}$  to  $+70^{\circ}$  C unless otherwise specified.

<sup>†</sup> For bus pins, see III under specification group II.

DC005 (Specification Group IV - Ternary State Inputs)

| Parameter                  |        |                                     | F    | Requirem |      |  |

|----------------------------|--------|-------------------------------------|------|----------|------|--|

| Name                       | Symbol | Conditions <sup>1</sup>             | Min  | Max      | Unit |  |

| Low-level input voltage    | VIL    | (See Fig. 10A)                      |      | 0.3      | ٧    |  |

| High-level input voltage   | ViH    | (See Fig. 10A)                      | 4.75 |          | ٧    |  |

| Open circuit input voltage | Vor    | 4.75 <v<sub>cc<br/>&lt;5.25</v<sub> | 1    | 2        | ٧    |  |

$<sup>^1</sup>Ambient$  operating temperature (T\_A) = 0° to +70° C unless otherwise specified.

DC005 (Specification Group V - TTL Input with Pull-Down)

| Parameter                                     |                 |                                                                        | R   | Requirement |      |  |

|-----------------------------------------------|-----------------|------------------------------------------------------------------------|-----|-------------|------|--|

| Name                                          | Symbol          | Conditions <sup>1</sup>                                                | Min | Max         | Unit |  |

| High-level input<br>voltage                   | ViH             | (See Fig. 10A)                                                         | 2   |             | ٧    |  |

| Low-level input voltage                       | VIL             | (See Fig. 10A)                                                         |     | 0.8         | ٧    |  |

| input ciamp<br>voltage                        | Vı              | $V_{cc} = 4.75 \text{ V}$<br>$I_1 = -18 \text{ mA}$<br>(See Fig. 10C)  |     | -1.2        | ٧    |  |

| High-level input<br>current                   | Ін              | $V_{cc} = 5.25 \text{ V}$<br>$V_i = 2.4 \text{ V}$<br>(See Fig. 10D)   |     | 1.2         | mA   |  |

| Low-level input voltage forcing input current | VII             | $V_{cc} = 4.75 \text{ V}$<br>I <sub>I</sub> = 0.1 mA<br>(See Fig. 10H) |     | 0.8         | ٧    |  |

| Input current at low-level                    | l <sub>1L</sub> | $V_{cc} = 5 \text{ V}$<br>$V_1 = 0.4 \text{ V}$<br>(See Fig. 10E)      | 50  | 200         | μА   |  |

$<sup>^</sup>t Ambient$  operating temperature (T\_a) = 0° to +70° C unless otherwise specified.

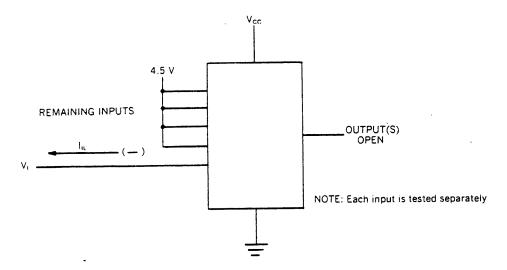

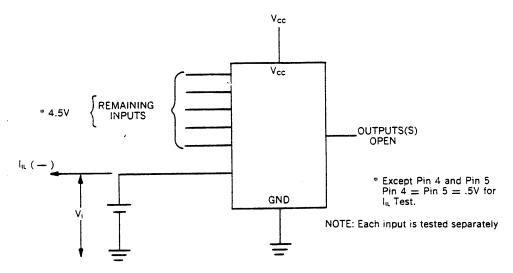

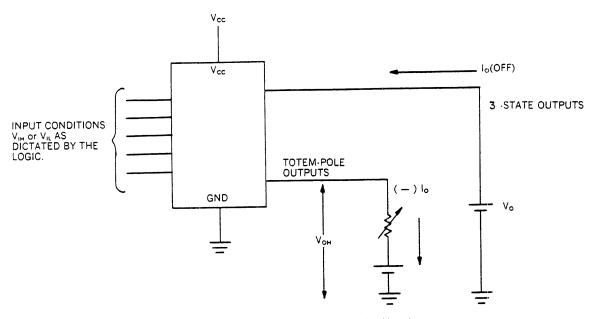

Figure 10A DC Test Circuit - VIH, VIL, VOH, IOH

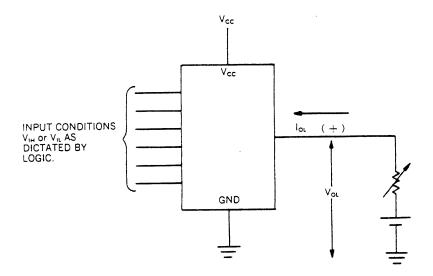

Figure 10B DC Test Circuit - VIH, VIL, Vol.

Figure 10C DC Test Circuit --- Vi

Figure 10D DC Test Circuit - II, IIH

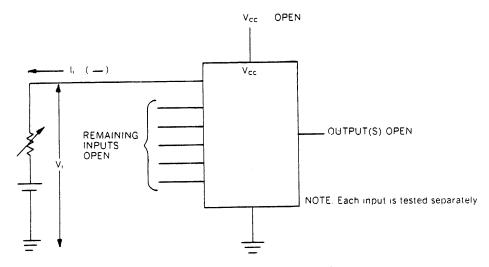

Figure 10E DC Test Circuit --- Inc

NOTE: Only one output be shorted at a time and the duration should not exceed more than a second.

Figure 10F DC Test Circuit — los

Figure 10G DC Test Circuit — Icc

Figure 10H DC Test Circuit - Vii

Figure 11 DC005 Timing Diagram

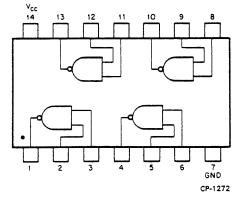

# DC006\_WORD COUNT/BUS ADDRESS LOGIC (DEC #19-14035-00)

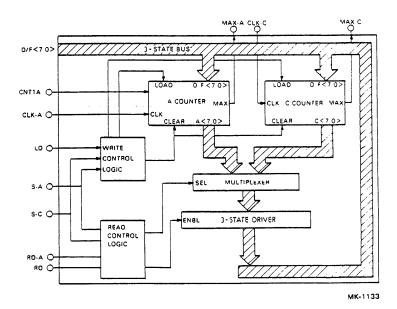

The word count/bus address (WC/BA) chip is a 20-pin, 0.762 cm center  $\times$  2.74 cm long (0.3 in center  $\times$  1.08 in long) DIP, low-power Schottky device. Its primary use is in DMA peripheral device interfaces. This IC is designed to connect to the 3-state side of the DC005 transceiver. The DC006 has two 8-bit binary up-counters, one for the word (byte) count and another for bus address. Two DC006 ICs may be cascaded to increase register implementation.

The chip is controlled by the address latch protocol chip (DC004), the DMA chip (DC010), and a minimum of ancillary logic. Both counters may be cleared simultaneously. Each counter is separately loaded by LD and the corresponding select line from the protocol chip. Each counter is incremented separately. The WC counter (word byte counter) is always incremented by one; the A counter (bus address) may be incremented by one or two for byte or word addressing, respectively.

Data from the DC006 IC is placed on the 3-state bus via internal 3-state drivers. Each counter is separately read by RD and the corresponding select line.

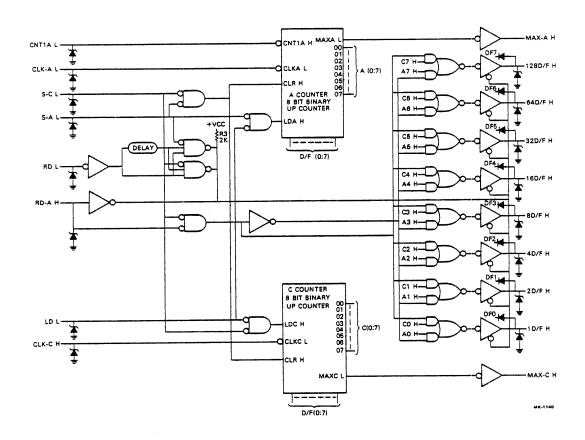

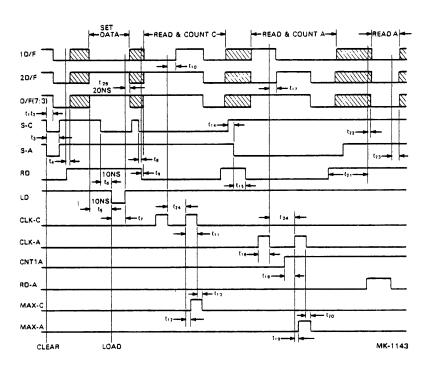

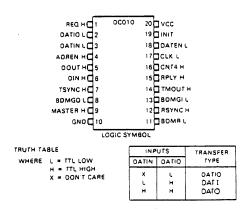

Figure 12 is a block diagram of the DC006 IC while Figure 13 illustrates a simplified logic diagram. Figures 15 and 16 illustrate input and output voltage waveforms. Figure 17 shows the timing diagram of the DC006 while the setup time and pulse width switching characteristics are presented in Tables 6 and 7. The DC006 pin/signal description is presented in Table 5. Figure 14 shows the various test conditions employed to derive the data presented in the Electrical Characteristics.

Figure 12 DC006 Simplified Block Diagram

| TRUTH TABLES |   |                         |

|--------------|---|-------------------------|

| WHERE        | L | = TTL LOW               |

|              | н | ≈ TTL HIGH              |

|              | X | ■ DON'T CARE            |

|              | Z | # HIGH IMPEDANCE        |

|              | 4 | # HIGH TO LOW TRANSITIO |

| READ CONTROL |      |     |       |                      |  |

|--------------|------|-----|-------|----------------------|--|

|              | INPL | JTS |       | OUTPUTS              |  |

| LD           | н    | S-A | s-c   | D/F<7:0>             |  |

| RD-A         | RD   | -   |       |                      |  |

| L            | L    | i,  | L     | CLEAR A&C AND READ C |  |

| L            | L    | L   | н     | A<7:0>               |  |

| L            | l i  | н   | l i   | C<7:0>               |  |

| Ĺ            | l L  | н   | н     | z -                  |  |

| L            | н    | ×   | ×     | Z                    |  |

| н            | lι   | L   | انا   | CLEAR A&C AND READ A |  |

| н            | L    | L.  | н     | A<7:0>               |  |

| н            | l L  | н   | 1     | A<7:0>               |  |

| н            | l L  | н   | Н     | A<7:0>               |  |

| н            | I н  | L   | ا ر ا | CLEAR A&C AND READ A |  |

| н            | н    | ١   | +     | A<7:0>               |  |

| н            | н    | н   | [     | A<7:0>               |  |

| н            | н    | н   | н     | A<7:0>               |  |

| MAX-A H   | 1  | 00006 | 20 | □ vcc    |

|-----------|----|-------|----|----------|

| S-AL      | 2  | 00000 | 19 | D s-c ∟  |

| CLK-A L   | 3  |       | 18 | Dro r    |

| RD-A H    | 4  |       | 17 | MAX-C H  |

| RD L □    | 5  |       | 16 | Crk-c r  |

| CNT1A L   | 6  |       | 15 | 128D/F H |

| 1 D/F H 🗆 | 7  |       | 14 | 640/FH   |

| 2 D/F H   | 8  |       | 13 | 32D/F H  |

| 4 D/F H   | 9  |       | 12 | 160/F H  |

| GND 🗆     | 10 |       | 11 | D 80/F H |

|           |    |       |    | ,        |

| WRITE CONTROL   |     |     |                     |  |  |

|-----------------|-----|-----|---------------------|--|--|

| INPL            | JTS |     |                     |  |  |

| RD A = L RD = H | S-A | s-c | FUNCTION            |  |  |

| ľ               |     |     |                     |  |  |

| •               | L   | L   | *ILLEGAL            |  |  |

| •               | L   | H   | LOAD A<7:0>         |  |  |

| •               | н   | L   | LOAD C <7:0>        |  |  |

| X               | . н | н   | WC BA NOT SELECTED  |  |  |

| н               | L   | l L | CLEAR BOTH COUNTERS |  |  |

| н               | L   | н   | LOADING DISABLED    |  |  |

| H               | н   | L   | LOADING DISABLED    |  |  |

<sup>\*</sup>ILLEGAL CONDITION BECAUSE A LOAD OPERATION AND A CLEAR OPERATION IS ATTEMPTED SIMULTANEOUSLY RESULT OF THIS CONDITION IS CLEAR.

Figure 13 DC006 Simplified Logic Diagram

Table 5 DC006 Pin/Signal Descriptions

| Pin | Signal   | Description                                                                                                                                                                                                                                                                                                                    |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | CNT1 A L | Count A Counter by 1 (TTL Input). This signal controls the least significant bit of the A counter. When CNT1A is low, the A counter increments by one. When high, the LSB is prevented from toggling, hence the counter increments by two. When two counters are cascaded, CNT1A on the high-order counter should be grounded. |

| 3   | CLK-A L  | Clock A Counter (TTL Input). This clock signal increments the A counter on its negative edge. The counter is incremented by one or two, depending on CNT1A. CNT1A and LD must be stable while CLK-A is high.                                                                                                                   |

| 16  | CLK-C L  | Clock C Counter (TTL Input). This clock signal increments the C counter by one on its negative edge. LD must be stable while CLK-C is high.                                                                                                                                                                                    |

| 2   | S-A L    | Select A Counter (TTL Input). This signal allows the selection of the A counter according to the truth tables (Figure 13).                                                                                                                                                                                                     |

| 19  | S-C L    | Select C Counter (TTL Input). This signal allows the selection of the C counter according to the truth tables (Figure 13).                                                                                                                                                                                                     |

| 4   | RD-A H   | Read A Counter (TTL Input). This signal allows the selection of the A counter according to the truth tables (Figure 13).                                                                                                                                                                                                       |

| 5   | RD L     | Read (TTL Input). This signal allows the read operation to take place according to the truth tables (Figure 13).                                                                                                                                                                                                               |

| 18  | LD L     | Load (TTL Input). When this signal goes through a high-to-low transition, the load operation is allowed to take place according to the truth tables (Figure 13). No data changes permitted while LD is low.                                                                                                                    |

Table 5 DC006 Pin/Signal Descriptions (Cont)

| Pin          | Signal      | Description                                                                                                                                                                         |

|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-9<br>11-15 | D/F (7:0) H | Data Bus (Bidirectional, 3-State Outputs/<br>TTL Inputs). These eight bidirectional lines<br>are used to carry data in and out of the<br>selected counter.                          |

| 1            | мах-а н     | Maximum A Count (TTL Output). This signal is generated by ANDing CLK-A and the maximum count condition of counter A (count 376 when counting by 2 or count 377 when counting by 1). |

| 17           | MAX-C H     | Maximum C Count (TTL Output). This signal is generated by ANDing CLK-C and the maximum count conditions of counter C (count 377).                                                   |

DC006 Electrical Characteristics

DC006 TTL (TTL Input and Output Pins)

| Parameter                                                                             |          |                                                                        | Re  | quireme             | nts                      |

|---------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------|-----|---------------------|--------------------------|

| Name                                                                                  | Symbol   | Conditions*                                                            | Min | Max                 | Unit                     |

| High-level input voltage                                                              | Vін      | (See Fig. 14A,<br>14B)                                                 | 2   |                     | ٧                        |

| Low-level input voltage                                                               | VIL      | (See Fig. 14A,<br>14B)                                                 |     | 8.0                 | ٧                        |

| Input clamp<br>voltage                                                                | Vı       | $V_{cc} = Open$<br>$I_1 = -18 \text{ mA}$<br>(See Fig. 14C)            |     | 1.2                 | <b>V</b>                 |

| High-level output voltage                                                             | Vон      | $V_{cc} = 4.75 \text{ V}$<br>$I_0 = -1 \text{ mA}$<br>(See Fig. 14A)   | 2.7 |                     | ٧                        |

| Low-level output<br>voitage                                                           | VoL      | $V_{cc} = 4.75 \text{ V}$<br>$I_0 = 20 \text{ mA}$<br>(See Fig. 148)   |     | 0.5                 | ٧                        |

| Input current at maximum input voltage                                                | lı .     | $V_{cc} = 5.25 \text{ V}$<br>$V_i = 5.5 \text{ V}$<br>(See Fig. 14D)   |     | 1                   | mA                       |

| High-level input<br>current<br>Except 3-state<br>3-state pin                          | Іін      | $V_{cc} = 5.25 \text{ V}$<br>$V_1 = 2.7 \text{ V}$<br>(See Fig. 14D)   |     | 50<br>55            | μ <b>Α</b><br>μ <b>Α</b> |

| Low-level input<br>current<br>CLKA, CLKC<br>CNTIA<br>D/F(7:0),LD,RD,<br>SC,SA<br>RD-A | lic      | $V_{cc} = 5.25 \text{ V}$<br>$V_{t} = 0.5 \text{ V}$<br>(See Fig. 14E) |     | -1.1<br>-1.7<br>100 | mA<br>mA<br>μA           |

| Off-state high impedance state—output current 3-state only                            | lo (OFF) | $V_{cc} = 5.25 \text{ V}$<br>$V_0 = 3.75 \text{ V}$<br>(See Fig. 14A)  |     | 100                 | μΑ                       |

| Short-circuit output current                                                          | los      | Vcc = 5.25 V†<br>(See Fig. 14F)                                        | -40 | -100                | mA                       |

| Supply current                                                                        | lcc      | $V_{cc} = 5.25 \text{ V}$ (See Fig. 14G)                               |     | 170                 | mA                       |

<sup>\*</sup>Ambient operating temperature (T<sub>A</sub>) = 0° to +70° C; Vcc = 5.0  $\pm$  0.25 unless otherwise specified.

<sup>†</sup> Not more than one output shall be shorted at a time and the duration shall not exceed 1 second.

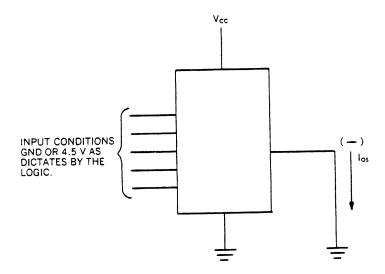

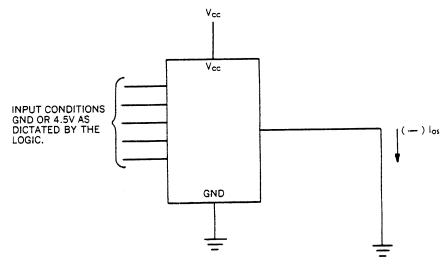

Figure 14A DC Test Circuit (VIH, VIL, VOH, lo(OFF)

Figure 14B DC Test Circuit (VIH, VIL, VOL)

Figure 14C DC Test Circuit (V<sub>I</sub>)

Figure 14D DC Test Circuit (li, lin)

Figure 14E DC Test Circuit (In)

NOTE: Only one output should be shorted at a time, and the duration should not exceed more than a second.

Figure 14F DC Test Circuit (los)

Figure 14G DC Test Circuit (lcc)

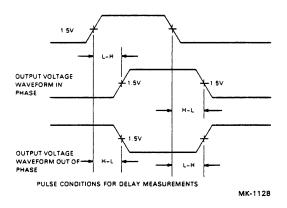

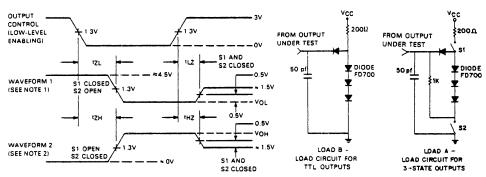

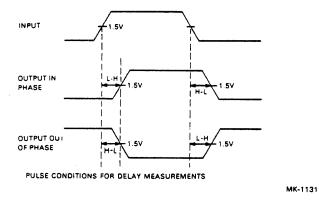

Figure 15 Input Voltage Waveform

NOTES

1 WAVEFORM 1 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS LOW EXCEPT WHEN DISABLED BY THE OUTPUT CONTROL.

MK-1130

Figure 16 Outputs Voltage Waveforms (3-State)

<sup>2</sup> WAVEFORM 2 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS HIGH EXCEPT WHEN DISABLED BY THE OUTPUT CONTROL

Figure 17 DC006 Timing Diagram

Table 6 Setup Time and Pulse Width Switching Characteristics\*

| Time            | Description             | Signal          | Min   |

|-----------------|-------------------------|-----------------|-------|

| t <sub>3</sub>  | Pulse width (min)       | S-C to S-A      | 50 ns |

| t <sub>5</sub>  | Setup time              | D/F (7:0) to LD | 10 ns |

| t <sub>6</sub>  | Setup time              | S-C to LD       | 10 ns |

| t <sub>7</sub>  | Pulse width (min)       | LD              | 90 ns |

| ta              | Setup time              | S-C to RD       | 20 ns |

| t <sub>11</sub> | Clock pulse width (min) | CLK-C (HI)      | 40 ns |

| t <sub>14</sub> | Setup time              | S-C to S-A      | 20 ns |

| t <sub>15</sub> | Setup time              | S-A to RD       | 10 ns |

| t <sub>16</sub> | Clock pulse width (min) | CLK-A (HI)      | 40 ns |

| tis             | Setup time              | CNT1A to CLK-A  | 45 ns |

| t <sub>21</sub> | Setup time              | RD to RD-A      | 15 ns |

| t <sub>24</sub> | Clock off time (min)    | CLK-A, CLK-C    | 40 ns |

| t <sub>25</sub> | Data hold time          | LD to DATA IN   | 20 ns |

$<sup>^{\</sup>circ}V_{CC} = 5.0 \pm 0.25 \text{ V}.$

Table 7 Switching Characteristics\*

|                                      | Input !        | Signal     | Output !       |             | Test                                 | Delay    |          |

|--------------------------------------|----------------|------------|----------------|-------------|--------------------------------------|----------|----------|

| Time                                 | Name           | Polarity   | Name           | Polarity    | Conditions                           | Min      | Max      |

| t <sub>1</sub>                       | S-C<br>S-A     | H-L<br>H-L | D/F (7:0)      | X-L         | Load A<br>RD-A = 0.4V<br>(C Counter) | 15       | 80       |

| t <sub>2</sub>                       | S-C<br>S-A     | H-L<br>H-L | D/F (7:0)      | X-L         | Load A<br>RD-A = 0.4V<br>(A Counter) | 15       | 80       |

| t <sub>4</sub>                       | RD             | L-H        | D/F (7:0)      | D/F (7:0)-Z | Load A                               | 10       | 30       |

| t <sub>9</sub>                       | RD             | H-L        | D/F (7:0)      | Z-D/F (7:0) | Load A                               | 34       | 80       |

| t <sub>10</sub>                      | CLK-C          | H-L        | D/F 1          | L-H         | Load A                               | 18       | 55       |

| t <sub>12</sub> ,<br>t <sub>19</sub> | CLK-C<br>CLK-A | L-H        | MAX-C<br>MAX-A | L-H         | Load B                               | 10       | 35       |

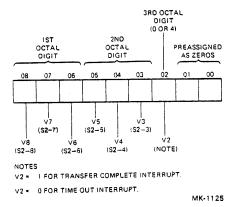

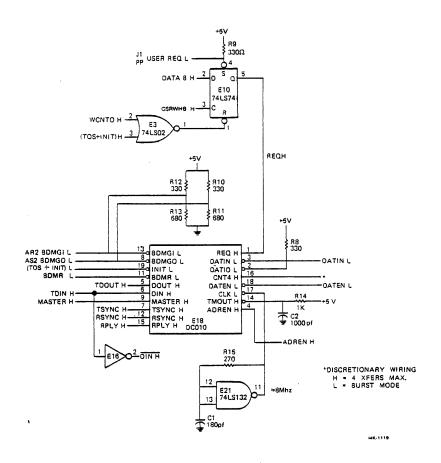

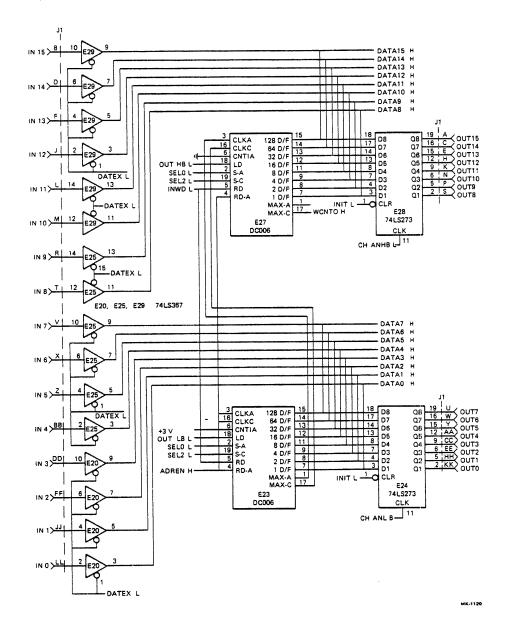

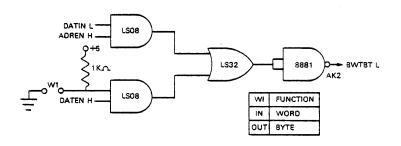

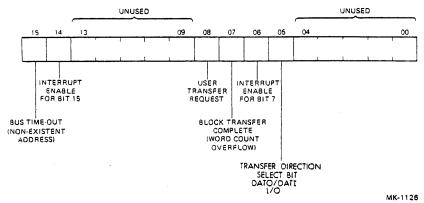

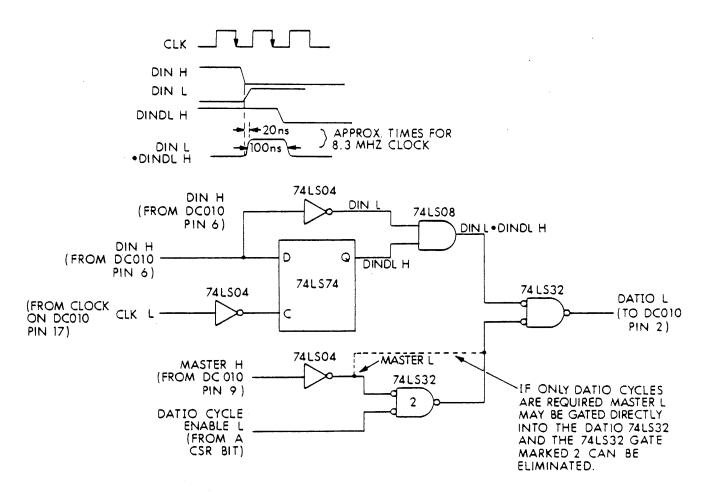

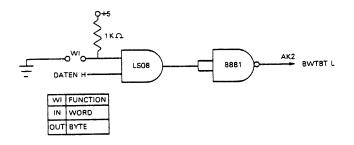

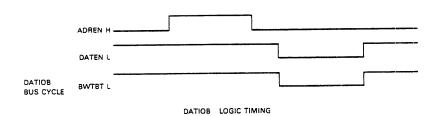

| t <sub>13</sub>                      | CLK-C          | H-L        | MAX-C          | H-L         | Load B                               | 10       | 35       |